FPGA设计系统时钟的影响因素及其分析

co+T2max,其中T3为D2的建立时间Tset,T2为组合逻辑的延时。在一个设计中T3和Tco都是由器件决定的固定值,可控的也只有T2也就时输入端组合逻辑的延时,所以通过尽量来减小T2就可以提高系统的工作时钟。为了达到减小T2在设计中可以用下面不同的几种方法综合来实现。

1.2.1 通过改变走线的方式来减小延时

以altera的器件为例,我们在quartus里面的timing closure floorplan可以看到有 很多条条块块,我们可以将条条块块按行和按列分,每一个条块代表1个LAB,每个LAB里 有8个或者是10个LE。它们的走线时延的关系如下:同一个LAB中(最快) 同列或者同行 不同行且不同列。 我们通过给综合器加适当的约束(约束要适量,一般以加5%裕量较为合适,比如电路 工作在100Mhz,则加约束加到105Mhz就可以了,过大的约束效果反而不好,且极大增加综合时间)可以将相关的逻辑在布线时尽量布的靠近一点,从而减少走线的时延。

1.2.2 通过拆分组合逻辑的方法来减小延时

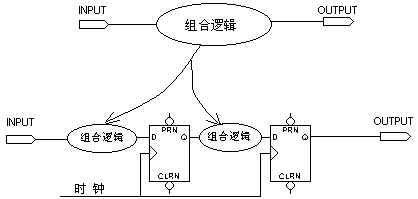

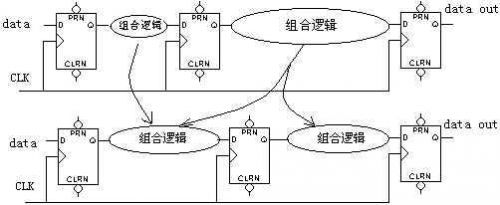

由于一般同步电路都不止一级锁存(如图8),而要使电路稳定工作,时钟周期必须满足最大延时要求,缩短最长延时路径,才可提高电路的工作频率。如图7所示:我们可以将较大的组合逻辑分解为较小的几块,中间插入触发器,这样可以提高电路的工作频率。这也是所谓“流水线”(pipelining)技术的基本原理。

对于图8的上半部分,它时钟频率受制于第二个较大的组合逻辑的延时,通过适当的方法平均分配组合逻辑,可以避免在两个触发器之间出现过大的延时,消除速度瓶颈。

图7 分割组合逻辑

图8 转移组合逻辑

那么在设计中如何拆分组合逻辑呢,更好的方法要在实践中不断的积累,但是一些良好的设计思想和方法也需要掌握。我们知道,目前大部分FPGA都基于4输入LUT的,如果一个输出对应的判断条件大于四输入的话就要由多个LUT级联才能完成,这样就引入一级组合逻辑时延,我们要减少组合逻辑,无非就是要输入条件尽可能的少,这样就可以级联的LUT更少,从而减少了组合逻辑引起的时延。

我们平时听说的流水就是一种通过切割大的组合逻辑(在其中插入一级或多级D触发器,从而使寄存器与寄存器之间的组合逻辑减少)来提高工作频率的方法。比如一个32 位的计数器,该计数器的进位链很长,必然会降低工作频率,我们可以将其分割成4位和 8位的计数,每当4位的计数器计到15后触发一次8位的计数器,这样就实现了计数器的切割,也提高了工作频率。

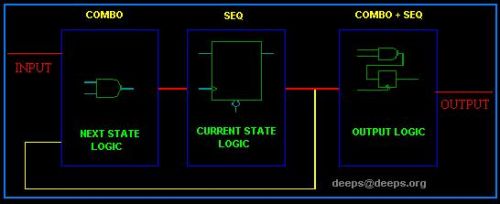

在状态机中,一般也要将大的计数器移到状态机外,因为计数器这东西一般是经常 是大于4输入的,如果再和其它条件一起做为状态的跳变判据的话,必然会增加LUT的级 联,从而增大组合逻辑。以一个6输入的计数器为例,我们原希望当计数器计到111100后 状态跳变,现在我们将计数器放到状态机外,当计数器计到111011后产生个enable信号 去触发状态跳变,这样就将组合逻辑减少了。状态机一般包含三个模块,一个输出模块,一个决定下个状态是什么的模块和一个保存当前状态的模块。组成三个模块所采用的逻辑也各不相同。输出模块通常既包含组合逻辑又包含时序逻辑;决定下一个状态是什么的模块通常又组合逻辑构成;保存现在状态的通常由时序逻辑构成。三个模块的关系如下图9所示。

图9 状态机的组成

所有通常写状态机时也按照这三个模块将状态机分成三部分来写,如下面就是一种良好的状态机设计方法:

/*-----------------------------------------------------

This is FSM demo program

Design Name : arbiter

File Name : arbiter2.v

-----------------------------------------------------*/

module arbiter2 (

clock , // clock

reset , // Active high, syn reset

req_0 , // Request 0

req_1 , // Request 1

gnt_0 ,

gnt_1);

//-------------Input Ports-----------------------------

input clock ;

input reset ;

input req_0 ;

input req_1 ;

//-------------Output Ports----------------------------

output gnt_0 ;

output gnt_1 ;

//-------------Input ports Data Type-------------------

wire clock ;

wire reset ;

wire req_0 ;

wire req_1 ;

//-------------Output Ports Data Type------------------

reg gnt_0 ;

reg gnt_1 ;

//-------------Internal Constants--------------------------

parameter SIZE = 3 ;

parameter IDLE = 3‘b001 ,

GNT0 = 3’b010 ,

GNT1 = 3‘b100 ;

//-------------Internal Variables---------------------------

reg [SIZE-1:0] state ;// Seq part o

- STM32学习笔记(3):系统时钟和SysTick定时器(11-28)

- C8051F340系统时钟配置(11-28)

- S5PV210(TQ210)学习笔记——系统时钟和串口(11-28)

- STM32学习笔记——RCC系统时钟配置(11-28)

- STM32 开发板入门教程 (三) 系统时钟 SysTick(11-28)

- stm32系统时钟配置问题(11-27)