电子系统级设计和验证方法学在SoC设计中的应用

制解调器。

2.快速验证

TLM的抽象级别明显高于RTL的抽象级别,它描述模块内的电路状态、精确到纳秒的转换以及精确到位的总线行为。因此,意法微电子等领先公司认为,相比使用RTL,使用周期精确的TLM将使硬件验证和硬件/软件协同验证速度快1,000倍或者更多。这种方法不仅可产生用于验证系统行为和RTL实现的功能测试基准(testbench),它还支持SystemC与RTL的协同仿真,这样SoC TLM可被当作一个“测试台”,当下游RTL实现模块可用时,它们便可在这个测试台上进行验证。

高通公司的经验表明,系统级的HW/SW协同验证要优于C/RTL实现级的HW/SW协同验证。一个维特比解码器设计可在20ms内执行一个信息包,但是在C/RTL级进行仿真却需要6个小时,高通估计必须仿真1,000个信息包才能达到合理的置信度,因此总共需要6,000小时的仿真时间,但这是不现实的。而1,000个信息包与一个TLM进行协同验证将只需要6个小时,或者更少。

针对应用优化的处理器的综合:不断增强的处理能力需求经常通过采用额外标准通用(GP)处理器内核来满足。然而,构建GP内核是用来解决广范围内的应用,它可能无法以必备的性能执行一个给定软件算法,且可能占用过多芯片面积和功率。另外,它通常还需支付大量的额外IP许可费和版权费。

采用指令集(IS)针对应用需求优化过的处理器可解决这个问题。定制IS处理器可在只有绝对必要的硬件资源条件下提供必备的性能。利用ESL工具,这样的处理器可以从结构描述或者定制IS本身开始自动综合。ESL工具还自动生成处理器的软件开发工具,例如指令集仿真器、汇编器、链接器、反汇编器、调试器和C编译器。

以英飞凌为例,该公司据称在两个月内就为特定应用的多速率DSP开发出网表和开发工具。

3.先进算法开发

在消费设备中使用的诸如JPEG和MPEG等很多先进算法都是数字信号处理算法,必须实现这些算法以达到对不同设备来说可能不同的性能和功耗目标。先进算法通常首先设计成浮点算术形式的参考算法(实际上,像JPEG和MPEG这样的标准算法一般都以这种形式实现),然后再转换成定点算术形式,嵌入式软件和RTL实现便是从定点算术形式衍生出来的。

针对DSP算法的图形化ESL设计以及仿真工具能实现这种流程。对于通信和多媒体应用,采用可定制DSP算法的预设计库能加速算法开发。另外还存在一些标准算法库,例如3G W-CDMA、GSM/EDGE、IS-95 CDMA、IEEE 802.11/a/b/g 无线局域网(WLAN)、蓝牙和UWB。当HW/SW分割后,采用微架构库可加速RTL实现的开发。大唐使用这样的工具与其他公司合作开发了TD-SCDMA的基带库。

TLM方法论

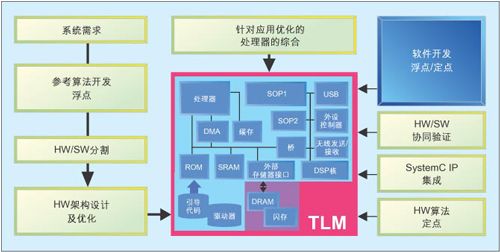

TLM是可实现及早开始软件开发、ESL设计以及验证任务的虚拟集成平台,图2显示了TLM在SoC设计中所处的中心位置。

图2:ESL设计与验证任务。

SoC TLM本质上是器件资源的一个网络模型,它全无实现的细节。功能模块的行为模型是根据它们的输入激励和输出响应来建立的。模块通过由API连接至每个模块的一个或者一组总线进行通信,这些通信过程则被建模成具有相关数据传输的数据流机制。这样避免了不必要的实现细节,这些细节会模糊设计工程师的系统行为视图并减慢仿真速度。模块行为与通信分开,可实现功能模块的快速修改或者替换而无需重新设计总线,反之亦然,它对快速的IP集成以及复杂的“what if”分析也非常关键。

有三种常见的TLM使用模式:程序员视图(PV)、架构师视图(AV)以及验证视图(VV)。尽管这些模式代表三种不同的系统视图,但是大多数模型都能以所有三种模式进行配置。

1.程序员视图

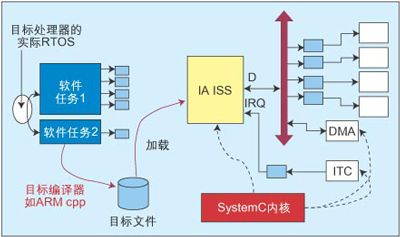

程序员视图TLM是SoC的一种功能正确模型,它允许使用传统软件以及及早开发新软件。一般情况下,PV TLM由处理器、存储器、外设的功能模型以及将事务引导到正确存储器或外设的路由器功能模型组成(见图3)。

图3:程序员视图TLM。

PV使软件开发人员能够访问必需的系统资源和属性,比如寄存器的可见性、寄存器的精确性和中断处理等,同时它还可直接链接目标处理器和调试环境的指令集仿真器(ISS)。目标RTOS的API以及目标处理器的编译器用来开发软件对象代码,此阶段的应用软件开发只需一个数据流模式(schema)。因此,PV是不定时的,PV仿真可在每秒数百万条指令的速度范围内很好地执行。

2.架构师视图

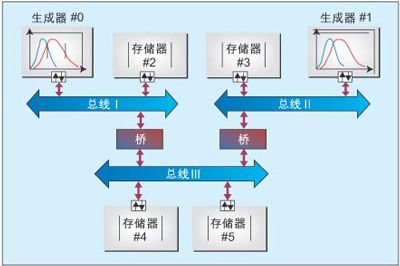

架构师视图TLM是具有SoC时序属性的相同模型。该模型使设计团队能够分析SoC性能以便在设计实 现之前准确找出瓶颈(见图4)。最终的硬件/软件分割决定是在这个视图中实现的。

图4:架构师视图TLM。

时序的捕获不是显式就是隐式。显式时序可以近似地模仿SoC的硬件性能,它用系统事件和事件同步

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)