基于ATE的FPGA测试方法

时间:06-06

来源:互联网

点击:

1 引言

随着集成电路技术的发展,现场可编程门阵列FPGA(Field Programmable Gate Array)器件的应用越来越广泛,其测试技术也得到了广泛重视和研究。FPGA的测试可分为面向制造的测试过程(MTP)和面向应用的测试过程(ATP)两类。MTP主要是从制造商的角度来测试,测试成本主要体现在测试向量集长度所决定的测试时间的费用上。MTP主要针对可编程逻辑块(CLB)、输入输出单元(10B)、可编程连线(PI)及编程用的SRAM等进行测试。ATP是在应用级上的测试,也就是把FPGA配置为特定的功能进行测试,具有很强的针对性,测试过程相对简单。国内的研究大多集中在MTP,且主要用于自主搭建的测试系统,可移植性差。本研究基于J750测试系统用Xilinx 4010为研究对象,使用两种简单的电路,即可完成对LUT、进位逻辑、D触发器的测试,而且修改方便,可移植性好,为FPGA的通用测试提供了一种方法切实可行的有效方法。

2可编程逻辑资源测试

2.1 可编程逻辑资源(CLB)

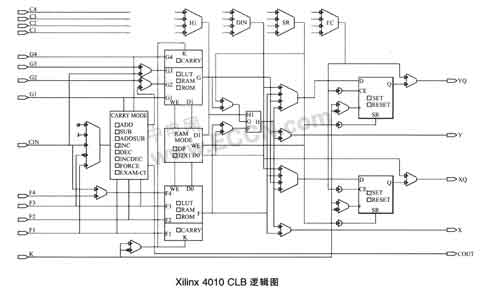

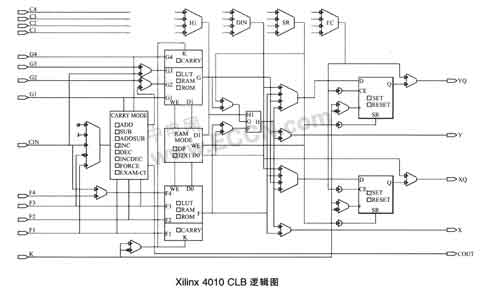

可编程逻辑功能块实现FPGA中的逻辑功能,是FPGA的主要部件,Xilinx 4010 CLB的基本逻辑结构如图1所示。从图中可以看出,CLB主要是由两个查找表(LUT),一个进位逻辑,两个D触发器及一些多路选择开关组成。

2.2单个CLB逻辑资源的覆盖

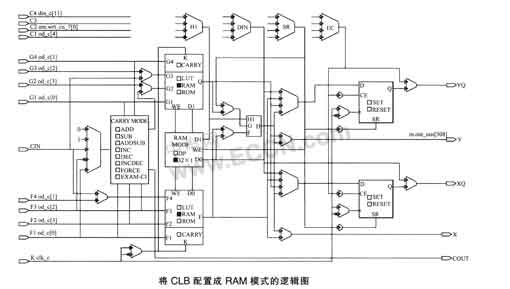

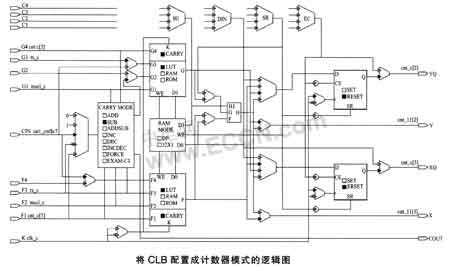

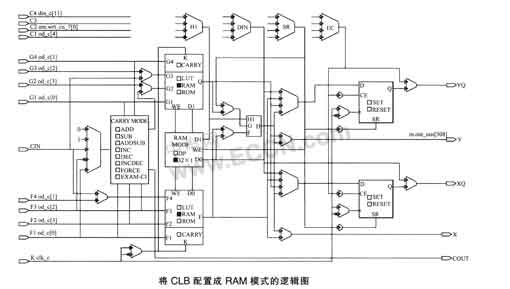

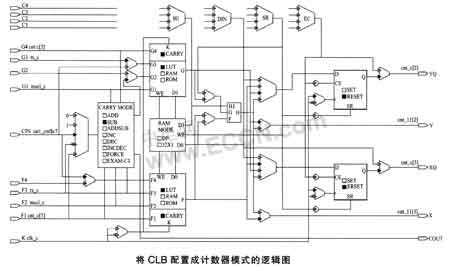

由于CLB能实现的逻辑功能较多,通过对CLB的一次编程来完全覆盖其功能是不可能的,但穷尽每一种逻辑来验证CLB的功能也是不可能的,因此我们根据CLB的逻辑结构设计几种测试配置,能够覆盖CLB的大部分功能。对于4010来说,CLB的测试需覆盖F函数G函数的RAM模式、LUT模式、进位逻辑功能及D触发器,至于多路选择器,将其配制在这几个模式里即可。因此,实现对CLB的测试.将CLB分别配置成RAM模式和计数器模式,可基本覆盖CLB的逻辑资源,如图2、图3所示。其中红线为配置后的电路,绿线为没有配置到的部分。

从图2可以看出,将CLB配置成RAM模式,实现了F函数、G函数的RAM功能(由于ROM模式包含在RAM模式中,因此不用再单独测试ROM模式),覆盖了除进位逻辑和D触发器外的其他逻辑单元。

从图3可以看出,将CLB配置成计数器模式,实现了F函数和G函数的LUT功能,覆盖进位逻辑和D触发器。

综上所述,用这两种电路,可以覆盖CLB中除多路选择器外的所有逻辑资源,基本覆盖CLB的输入输出。因此,用这两种电路可以实现对CLB的测试。

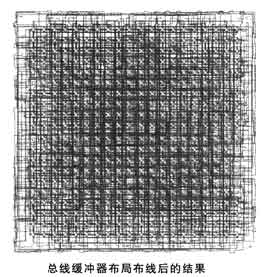

2.3 CIB阵列的测试配置

由于FPGA中CLB都是规则排列的,4010为20*20个CLB。为了提高测试效率,减少对CLB的编程次数,需要合理配置CLB。由于IOB资源的限制,不可能一次覆盖所有的CLB单元,需要进行多次配置,直至测完所有的CLB。由于每一次测试CLB的数目受限于CLB的配置和IOB的数目,因此CLB测试的重点就集中在CLB的配置,即如何合理配置CLB电路,达到既能覆盖电路的大部分功能,又减少了编程次数。这里,通过将FPGA配置成总线缓冲器,一次即可覆盖390个CLB,如图4所示。从下图可以看出,只需2次配置即可完成CLB阵列RAM功能的测试,第二次配置时,在第一次配置的基础上手工修改布局后自动布线即可。图中黄方块即为配置到的CLB模块,白块为没有配置到的CLB模块。

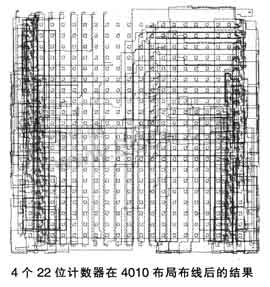

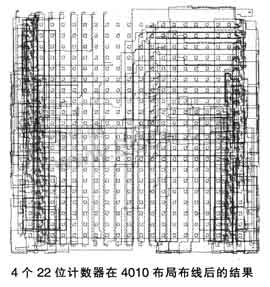

将FPGA配置成计数器,其测试速度取决于计数器的位数,位数越高,占用的CLB资源越多,配置次数就会越少,但测试时间会呈指数增长,因此,需要在测试时间和计数器位数上进行合理选择。经过计算,我们选择用22位计数器来配置CLB阵列,其布局布线后的结果如图5所示。从该图可以看出,这种配置方式仅仅占用16个CLB,25个IOB,为了提高测试速度.可以将n个计数器放置在一个FPGA中,进行并行测试,这样测试速度可以提高n倍。图5所示的就是4个22位计数器配置在一个FPGA中布局布线后的结果。

按照图5所示,共需要10次配置就可完成对CLB进位逻辑、D触发器及LUT功能的测试。在测试时只要给完整的测试码,故障覆盖率即可达到98%以上。

3基于ATE的FPGA测试

目前测试FPGA一般有两种手段:一种是自主研制测试系统,功能应包括配置FPGA、加载测试向量、读取测试响应等。该方法往往投资大,耗时长,测试精度难以保证,而且研制出来的测试平台可移植性差,只能用于研究和验证。另一种手段是用ATE来测试FPGA,先对]FPGA进行配置,然后对配置成的电路进行测试。这样可以在同一个操作流程中完成FPGA芯片的多次配置一测试过程,减少操作环节,提高FPGA芯片的测试效率,能够实现FPGA芯片的产业化测试。目前商用ATE的性能不断提高,本文以Teradyne应用最为广泛的J750为测试平台,该机测试管脚数可达1024个,测试向量的存储空间大,测试频率可以达到100MHz,完全能够满足市场上多数FPGA的测试要求。要快速有效的开发FPGA的测试程序,就要解决的难题是如何利用ATE对FPGA进行配置,将FPGA的配置文件转换成测试系统可执行的测试向量。

3.1 FPGA的配置过程

FPGA的配置是加载设计规定的编程数据到一个或多个器件的运行过程,以定义器件内部功能块和其互连的功能。Xilinx 4010器件的加电配置过程有四个主要的步骤:清除配置存储器、初始化、配置和启动。用ATE对FPGA进行在线配置主要采用从串模式,其配置过程的时序要求如下:芯片供电稳定后,进入配置前的准备状态,INIT端口输出低电平,时间为Tpor;INIT管脚变高再经过Tlcck后,可以对芯片进行配置,对CCLK和DIN管脚提供配置时钟和配置数据信号,配置时钟周期为TcclK,配置数据在CCIK的下降到来时给出。当所有配置数据被FPGA成功接受并且配置正确后,芯片开始进入Stan-uP进程,输出管脚DONE由低变为高,还应为CCLK提供至少六个周期的时钟信号,并对DIN提供高电平信号。Start-up进程结束后,不需再对CCLK和DIN提供信号,芯片的配置过程

完成。

3.2生成对FPGA进行配置的测试向量

由FPGA的设计开发工具生成的被测FPGA器件的配置文件为位流文件。位流文件的数据由起始码和程序数据组成。起始码包含起始序列位和被配置器件需要的配置数据位数的长度计数,程序数据包含被配置器件的配置信息。从配置文件中提取配置信息,并进行数据转换,就得到DIN管脚的配置数据信号。根据FPGA配置要求,设置FPGA的CCIK、INIT、DONE等控制管脚的逻辑状态。根据FPGA器件的配置过程对各管脚的时序要求,设置各个管脚的时序信息,得到配置过程的测试向量。这样FPGA的配置过程就可以作为一项功能测试由ATE执行。

3.3测试配置实现的电路

完成配置过程的FPGA芯片具有一定的功能,其测试方法与其他数字集成电路的测试方法类似,可以进行直流参数测试和功能测试。在J750上测试FPGA时,把配置也作为一个测试项,可以实现FP-GA的高速在线配置。配置完成后,对配置好的电路施加测试向量,完成测试过程。

4结论

本文以Xilinx 4010为例,用两种电路实现了对CLB的测试,并在Teradyne商用ATE上成功实现快速有效的配置一测试。该测试方法和配置测试过程可移植性好、通用性强,对于实现FPGA的产业化测试具有重要的意义。

随着集成电路技术的发展,现场可编程门阵列FPGA(Field Programmable Gate Array)器件的应用越来越广泛,其测试技术也得到了广泛重视和研究。FPGA的测试可分为面向制造的测试过程(MTP)和面向应用的测试过程(ATP)两类。MTP主要是从制造商的角度来测试,测试成本主要体现在测试向量集长度所决定的测试时间的费用上。MTP主要针对可编程逻辑块(CLB)、输入输出单元(10B)、可编程连线(PI)及编程用的SRAM等进行测试。ATP是在应用级上的测试,也就是把FPGA配置为特定的功能进行测试,具有很强的针对性,测试过程相对简单。国内的研究大多集中在MTP,且主要用于自主搭建的测试系统,可移植性差。本研究基于J750测试系统用Xilinx 4010为研究对象,使用两种简单的电路,即可完成对LUT、进位逻辑、D触发器的测试,而且修改方便,可移植性好,为FPGA的通用测试提供了一种方法切实可行的有效方法。

2可编程逻辑资源测试

2.1 可编程逻辑资源(CLB)

可编程逻辑功能块实现FPGA中的逻辑功能,是FPGA的主要部件,Xilinx 4010 CLB的基本逻辑结构如图1所示。从图中可以看出,CLB主要是由两个查找表(LUT),一个进位逻辑,两个D触发器及一些多路选择开关组成。

2.2单个CLB逻辑资源的覆盖

由于CLB能实现的逻辑功能较多,通过对CLB的一次编程来完全覆盖其功能是不可能的,但穷尽每一种逻辑来验证CLB的功能也是不可能的,因此我们根据CLB的逻辑结构设计几种测试配置,能够覆盖CLB的大部分功能。对于4010来说,CLB的测试需覆盖F函数G函数的RAM模式、LUT模式、进位逻辑功能及D触发器,至于多路选择器,将其配制在这几个模式里即可。因此,实现对CLB的测试.将CLB分别配置成RAM模式和计数器模式,可基本覆盖CLB的逻辑资源,如图2、图3所示。其中红线为配置后的电路,绿线为没有配置到的部分。

从图2可以看出,将CLB配置成RAM模式,实现了F函数、G函数的RAM功能(由于ROM模式包含在RAM模式中,因此不用再单独测试ROM模式),覆盖了除进位逻辑和D触发器外的其他逻辑单元。

从图3可以看出,将CLB配置成计数器模式,实现了F函数和G函数的LUT功能,覆盖进位逻辑和D触发器。

综上所述,用这两种电路,可以覆盖CLB中除多路选择器外的所有逻辑资源,基本覆盖CLB的输入输出。因此,用这两种电路可以实现对CLB的测试。

2.3 CIB阵列的测试配置

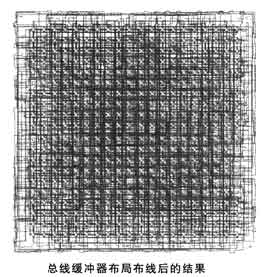

由于FPGA中CLB都是规则排列的,4010为20*20个CLB。为了提高测试效率,减少对CLB的编程次数,需要合理配置CLB。由于IOB资源的限制,不可能一次覆盖所有的CLB单元,需要进行多次配置,直至测完所有的CLB。由于每一次测试CLB的数目受限于CLB的配置和IOB的数目,因此CLB测试的重点就集中在CLB的配置,即如何合理配置CLB电路,达到既能覆盖电路的大部分功能,又减少了编程次数。这里,通过将FPGA配置成总线缓冲器,一次即可覆盖390个CLB,如图4所示。从下图可以看出,只需2次配置即可完成CLB阵列RAM功能的测试,第二次配置时,在第一次配置的基础上手工修改布局后自动布线即可。图中黄方块即为配置到的CLB模块,白块为没有配置到的CLB模块。

将FPGA配置成计数器,其测试速度取决于计数器的位数,位数越高,占用的CLB资源越多,配置次数就会越少,但测试时间会呈指数增长,因此,需要在测试时间和计数器位数上进行合理选择。经过计算,我们选择用22位计数器来配置CLB阵列,其布局布线后的结果如图5所示。从该图可以看出,这种配置方式仅仅占用16个CLB,25个IOB,为了提高测试速度.可以将n个计数器放置在一个FPGA中,进行并行测试,这样测试速度可以提高n倍。图5所示的就是4个22位计数器配置在一个FPGA中布局布线后的结果。

按照图5所示,共需要10次配置就可完成对CLB进位逻辑、D触发器及LUT功能的测试。在测试时只要给完整的测试码,故障覆盖率即可达到98%以上。

3基于ATE的FPGA测试

目前测试FPGA一般有两种手段:一种是自主研制测试系统,功能应包括配置FPGA、加载测试向量、读取测试响应等。该方法往往投资大,耗时长,测试精度难以保证,而且研制出来的测试平台可移植性差,只能用于研究和验证。另一种手段是用ATE来测试FPGA,先对]FPGA进行配置,然后对配置成的电路进行测试。这样可以在同一个操作流程中完成FPGA芯片的多次配置一测试过程,减少操作环节,提高FPGA芯片的测试效率,能够实现FPGA芯片的产业化测试。目前商用ATE的性能不断提高,本文以Teradyne应用最为广泛的J750为测试平台,该机测试管脚数可达1024个,测试向量的存储空间大,测试频率可以达到100MHz,完全能够满足市场上多数FPGA的测试要求。要快速有效的开发FPGA的测试程序,就要解决的难题是如何利用ATE对FPGA进行配置,将FPGA的配置文件转换成测试系统可执行的测试向量。

3.1 FPGA的配置过程

FPGA的配置是加载设计规定的编程数据到一个或多个器件的运行过程,以定义器件内部功能块和其互连的功能。Xilinx 4010器件的加电配置过程有四个主要的步骤:清除配置存储器、初始化、配置和启动。用ATE对FPGA进行在线配置主要采用从串模式,其配置过程的时序要求如下:芯片供电稳定后,进入配置前的准备状态,INIT端口输出低电平,时间为Tpor;INIT管脚变高再经过Tlcck后,可以对芯片进行配置,对CCLK和DIN管脚提供配置时钟和配置数据信号,配置时钟周期为TcclK,配置数据在CCIK的下降到来时给出。当所有配置数据被FPGA成功接受并且配置正确后,芯片开始进入Stan-uP进程,输出管脚DONE由低变为高,还应为CCLK提供至少六个周期的时钟信号,并对DIN提供高电平信号。Start-up进程结束后,不需再对CCLK和DIN提供信号,芯片的配置过程

完成。

3.2生成对FPGA进行配置的测试向量

由FPGA的设计开发工具生成的被测FPGA器件的配置文件为位流文件。位流文件的数据由起始码和程序数据组成。起始码包含起始序列位和被配置器件需要的配置数据位数的长度计数,程序数据包含被配置器件的配置信息。从配置文件中提取配置信息,并进行数据转换,就得到DIN管脚的配置数据信号。根据FPGA配置要求,设置FPGA的CCIK、INIT、DONE等控制管脚的逻辑状态。根据FPGA器件的配置过程对各管脚的时序要求,设置各个管脚的时序信息,得到配置过程的测试向量。这样FPGA的配置过程就可以作为一项功能测试由ATE执行。

3.3测试配置实现的电路

完成配置过程的FPGA芯片具有一定的功能,其测试方法与其他数字集成电路的测试方法类似,可以进行直流参数测试和功能测试。在J750上测试FPGA时,把配置也作为一个测试项,可以实现FP-GA的高速在线配置。配置完成后,对配置好的电路施加测试向量,完成测试过程。

4结论

本文以Xilinx 4010为例,用两种电路实现了对CLB的测试,并在Teradyne商用ATE上成功实现快速有效的配置一测试。该测试方法和配置测试过程可移植性好、通用性强,对于实现FPGA的产业化测试具有重要的意义。

ATEFPGA测试 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)