带GPS授时的TMS320F2812数据采集系统

12位ADC,但是为了进一步提高系统的A/D转换精度,增加了片外外设ADS8361。ADS8361是2+2通道,16位的A/D转换器;它同ADS7861(12位)完全兼容,可以与F2812数字信号处理器直接接口使用。它是由四通道差分输入分成两组分别连接到独立的转换器上的,可以完成双信号的同时采集,最高转换速率可以达到500 kHz。它工作在50 kHz频率时具有极强的抗干扰能力,特别适合数据采集的高采样率要求的场合。此外,ADS8361还提供高速双串行接口,可以有效地减少软件开销,并且功耗非常低,只有150 mW。

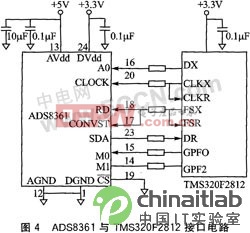

3.1 ADS8361与TMS320F2812接口电路设计

TMS320F2812处理器提供多通道缓冲串口(McBSP)和串行外设接口(SPI),两种串口都可以与ADS8361接口。根据设计的需要,本系统采用的是McBSP的接口扩展方式。在ADS8361与TMS320F2812的接口硬件设计时,为避免数据信号产生振铃,特意考虑在DSP与 ADS8361之间增加吸收电阻。由于TMS320F2812只有一个McBSP接口,因此必须将ADS8361设置在模式2和模式4。 TMS320F2812与ADS8361的硬件接口电路如图4所示,ADS8361的CLOCK、(RD+CONVST)和SDA引脚分别连接到 McBSP的CLKX、(FSX+FSR)和DR引脚。由于McBSP上只连接一个A/D转换芯片,片选信号(CS)直接接地,如果需要扩展多个A/D转换芯片,则可以采用GPIO控制片选信号;同时使用通用I/O控制ADS8361的工作模式,使M0=0,M1=1;DX控制ADS8361的通道选择。

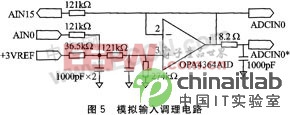

3.2 模拟输入信号调理电路的设计

电力系统的相电流和相电压分别经过CT和PT变换后,输出为标准±10 V的模拟电压信号。此模拟电压信号需要经过前端的低通滤波器,滤除不必要的高频噪声信号,以及将模拟输入信号范围由±10 V变换成后端A/D所能接受的信号范围。每一路的模拟调理电路如图5所示。

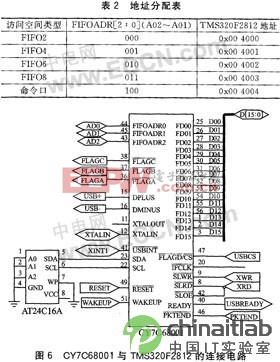

4 USB接口通信电路部分

通信电路采用USB接口,USB接口芯片选用Cypress公司的CY7C68001。CY7C68001与TMS320F2812的连接电路如图6所示。

CY7C68001作为TMS320F2812的外设,采用异步存储器接口与TMS320F2812相连接,上位PC机可以唤醒CY7C68001,也可以配置USB芯片。USBCS是CY7C68001的片选信号线,在USBCS为低电平时,CY7C68001采用异步读写方式完成二者之间的数据和命令的交换。

CY7C68001有两种对外接口,分别是FIFO数据接口和命令口。数据采集系统将这两种对外接口配置在地址范围是0x004000~0x004004 的空间,分配如表2所列。TMS320F2812通过CY7C68001的FIFO数据接口可以访问4个1 KB的FIFO中的数据,而FIFO数据接口的选择是通过控制地址线A[2:0]来实现的。当TMS320F2812的地址线A[2:0]为100B时,选中CY7C68001的命令口,然后通过命令口可以访问37个寄存器、Endpoint0缓冲器(64字节FIFO)和描述表(500字节FIFO)等。如果将Endpoint0缓冲器和描述表也看成寄存器,那么单个命令口内含了众多的寄存器,对这些寄存器进行读/写访问采用二次寻址方式,即首先通过命令口将要寻址的寄存器子地址和操作类型(读操作或写操作)写入,然后再通过命令口将数据读出或写入相应的寄存器。

CY7C68001还有一个中断信号USBINT和4个状态信号(USBREADY、FLAGA、FLAGB、和FLAGC)。中断信号USBINT占用 TMS320F2812的外部中断XINT1,状态信号USBREADY、FLAGA、FLAGB和FLAGC配置在另一个扩展的寄存器中, TMS320F2812可对其进行查询,从而得到USB的状态。USB芯片的WAKEUP也配置在另一个扩展的寄存器中,TMS320F2812通过对这个寄存器的写操作达到唤醒USB的目的。

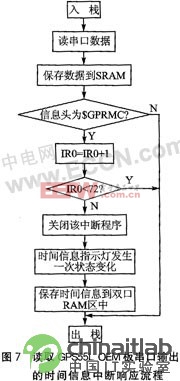

5 系统的软件部分

系统的软件部分包括主程序和各中断程序以及系统与上位PC机的USB通信程序。主程序完成各变量及串行口的初始化,并利用傅里叶变换算法计算出各采样点的实部和虚部。中断程序包括A/D转换程序、GPS时间信息的读取程序等。本文重点介绍用于读取GPS接收器串口输出的中断响应程序的设计思路,程序流程如图7所示。

6 电源设计

电源电路采用降额设计,并采用高精度电源电路,可保证供电系统的可靠性。

① ADS8361的内部参考电源为+2.5 V。

② GPS15L OEM板的供电电压为3.3~5.4 V,GPS接收天线的供电电压为3.0 V。

③ TMS320F2812要求双电源(1.9 V和3.3 V)为CPU、Flash、ROM、ADC和I/O接口供电。

当上电时,为了保证芯片内各个模块的正确复位,TMS320F2812供电需要满足一定的时序。该系统先给所有+3.3 V的电源引脚(VDDIO、VDD3VFL、VDDA1、VDDA2、VDDREF)上电,再接通1.9 V(VDD、VDD1)的芯片内核电源;当VDDIO的电压上升到2.5 V时,VDD才上升到0.3 V,这样才能保证片内各个模块上电时能正确复位。掉电时,在VDD下降到1.5

- 基于DSP2812的带式输送机多路温度检测系统设计(06-18)

- USB接口多路高速数据采集系统在LABVIEW平台的设计(11-08)

- TMS320F2812在井下微弱瓦斯信号检测的应用(03-25)

- 宽带阻抗测量仪的设计——微处理器电路设计(01-20)

- 基于DSP的数字存储示波器的设计方案(03-23)

- 基于TMS320F2812泄漏电流测试系统的设计(04-23)