数据采集的设计权衡

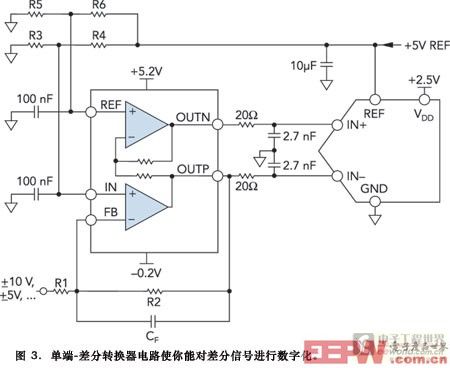

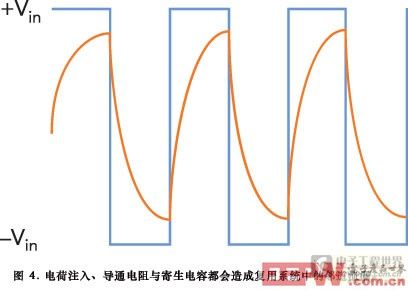

出了给定位数下需要多少过采样才能提高噪声性能的情形。 对给定位数提高噪声性能需要的过采样值 低压 ADC 与运放要求有足够的供电电流,才能在数据转换期间保持信号稳定。Hyde 说:“设计者挑选的运放和电压基准经常没有足够的驱动能力。一个电压基准可能同时需要流出和流入电流。”一个 ADC 可能有一个动态输入阻抗,而且可能需要一个低阻抗信号源作充分的耦合,才能维持基准电压电平。 National Instruments 的模拟设计工程师 Luis Orozco 称:“SAR 转换器需要一种很低的输出阻抗源来保持输入信号在转换期间不会变化。由于 SAR ADC 一般对其电源表现为高动态负载,我们要小心地旁路所有器件。”他指出,给一个 ADC 配用正确的运放非常重要。 Orozco 说:“一个运放要具备实现特定 ADC 规格的性能,它消耗的电流要比 ADC 自身多数倍。”ADC 的基准输入与信号输入表现类似。低功耗器件(如电压基准)可能需要电容器或缓冲器,从而在 ADC 对基准采样时保持输出的稳定电平。 Ivchenko 补充说:“不仅如此,还应采用低等效串联电阻(ESR)的旁路电容。可能的话尽量用 X7R 陶瓷电容,而不用钽电容。电容器必须有足够快的充放电速度,才能在转换期间为 ADC 提供足够的峰值电流。”高 ESR 会增加电容器的充放电时间。 图 2 给出了提供充足电流的两种方法。在图 2a 中,一只电容器存储能量,当 ADC 需要更多电流来保持基准电压稳定时,电容为其供电。一般 22?F 的电容就够用了,但要查看ADC 数据手册来确认这一点。在图 2b 中,运放用于 ADC 电压基准的缓冲。运放给电压基准提供了高阻抗输入,同时其低阻抗输出能为 ADC 提供充足的电流。虽然运放方案更讲究,但它为 Vref 增加了一个偏置电压,这会增加系统噪声、功耗,而且成本也更高。 差分输入 为改善动态范围和噪声抑制能力,应在数据采集系统中采用差分输入。使用差分输入时(与单端输入相反),两根信号线上的任何信号都被共模抑制(CMR)放大器或 ADC 排除掉了。如果传感器输出是单端的,可使用一种单端-差分转换驱动电路(图 3)。数据采集系统可以设计为使用单端输入或差分输入。 很多数据采集系统都用一个复用器来增加通道。复用器中的电阻与电容会影响信号的完整性。例如,来自复用器的电荷注入会将 DC 信号转变为 AC 信号。导通电阻(Ron)与寄生电容相结合,就形成了一个低通滤波器,它有一个 RC 时间常数。图 4 表示如果时间常数相对于采样时间过长将会发生的事情。 这个系统错误可以很容易被测试。将一个复用数据采集系统中的两个相邻通道(如通道 0 和 1)连接到接近系统输入极限的 DC 电压上,如 +10V 和 -10V。接下来,在两个输入通道之间进行交替采样。开始对每个通道进行几次采样,并逐渐转为每通道一次采样,然后切换通道。 如果时间常数快于采样速率,则应看到二分之一采样速率的一个方波。但如果时间常数过长,则所得到的是一个类似的三角波,因为通道之间有电荷注入。 Analog Devices 公司的 Hyde 说:“Ron 应不大于几欧姆。数百欧的导通电阻对今天的多数数据采集应用而言太大了。”而 National Instruments 的 Orozco 主张,数百欧并不太大,因为上游运放有高输入阻抗。 Hyde 还指出,复用器的导通电阻会根据系统输入信号的幅度而变化。如果将通道从一个电压轨变到另一个电压轨,就需要了解通道的 RC 时间常数。当 Ron 随电压变化时,通道电容会产生一个随频率变化的阻抗。这些阻抗与电容一起构成了一个可变的低通滤波器,并造成失真。 Hyde 说:“通道必须落在 ADC 精度极限内,以防止电荷导致的错误。”新复用器的电容小于较老型号,他补充说。 技术数据 在设计数据采集系统时,当然要依赖于 ADC、运放和电压基准的数据手册。元器件制造商也会为自己的元件提供其他有价值的资源,如参考设计板(图 5)。通常情况下,可以购买一块参考设计板来评估元件,然后再将它们设计到自己的系统里。 数据手册也提供了设计与布局信息,但 Keithley 的 Cawley 发现,数据手册上的信息和参考设计板可能不一致。在设计一个 500 k 采样/秒、18 位的数据采集系统时,Cawley 使用数据手册中的设计信息,不过发现 ADC 产生的噪声在 3 与 7 LSB 之间(5 ?V/LSB)。他说:“当我转用参考设计推荐的布局时,噪声跌到了

Ivchenko 在 ADC 后加了一个“砖墙式”(120 dB/倍频程)数字有限脉冲响应(FIR)滤波器,以降低噪声并提取出感兴趣的频谱。然后,他提取一部分数据或作一个移动平均,使采样速率能为应用所接受。

数据采集 相关文章:

- 为什么要进行信号调理?(09-30)

- 利用软件工具实现数据的采集和分析 (09-28)

- 高精度微功耗数据采集系统设计与应用(11-03)

- 多通道数据采集系统(11-12)

- 在LabVIEW中驱动数据采集卡的三种方法(04-21)

- 基于dsPIC30F的高精度数据采集器的研制(10-23)