分析系统优化小电流测量(上)

测量电路中的不稳定性。然而,要意识到,连接和断开电缆都会在电路中产生电流。为了进行超低电流测量,可能有必要在改变测试电路的连接后等待几分钟至几个小时,使杂散电流衰减。图4中的图形显示的是以下条件下的偏移:1)SMU的Force HI端子上戴有金属帽;2)前置放大器上仅连接一根三轴电缆;3)通过吉时利7174A型小电流开关矩阵至探针台,“up”位置有一个探针。

图3. Append按钮

图4. 整个测试系统的偏移电流测量

在生成电流-时间图形时施加一个测试电压,重复该项测试,确定测量电路中的漏泄电流。在DUT的实际测量中,使用的是测试电压,而非零偏压。现在,将测量并绘制测试夹具和电缆中的任何漏流。如果漏流太高,可对测量电路进行调节,减小漏流。关于减小漏流的方法信息,请参见本文“漏流和保护”部分。

IV测量误差源及减小误差的方法

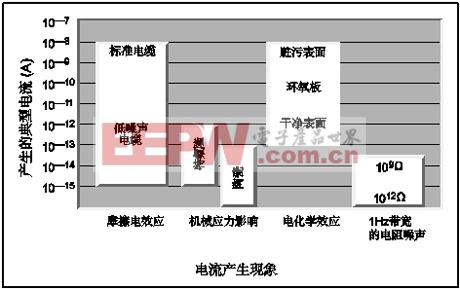

确定了电流偏移、漏流及所有不稳定性后,采取措施减小测量误差将有助于提高测量准确度。这些误差源包括建立时间不足、静电干扰、漏泄电流、摩擦效应、压电效应、污染、湿度、接地环路,以及源阻抗。图5中汇总了本节讨论的部分电流的幅值。

图5. 产生电流的典型幅值

建立时间和定时菜单设置

测量电路的建立时间在测量小电流和高电阻时尤其重要。建立时间是指施加或改变电流或电压后测量达到稳定的时间。影响测量电路建立时间的因素包括并联电容(CSHUNT)和源电阻(RS)。并联电容是由于连接电缆、测试夹具、开关和探针造成的。DUT的源电阻越高,建立时间越长。图6的测量电路中标出了并联电容和源电阻。

图6. 包含CSHUNT和RS的SMU测量电路

建立时间是RC时间常数τ的结果,其中:

τ = RSCSHUNT

以下为计算建立时间的一个例子,假设 CSHUNT = 10pF,RS = 1TΩ,那么:

τ = 10pF × 1TΩ = 10s

因此,读数稳定至最终值的1%所需的建立时间为τ的5倍,也就是50秒。图7所示为RC电路的阶跃电压指数响应。经过一个时间常数(τ = RC)后,电压上升至最终值的63%。

图7. RC电路的阶跃电压指数响应

为了成功测量小电流,重要的是每次测量留有足够的时间,尤其是扫描电压时。对于扫描模式,可在“ Sweep Delay”(扫描延迟)域的“Timing”(定时)菜单中添加建立时间;对于采样模式,则在“Interval time”域内。为了确定需要增加多长间隔时间,通过绘制电流-时间图,测量DUT稳定至某个阶跃电压的建立时间。阶跃电压应该是DUT实际测量中使用的偏执电压。可利用LowCurrent项目中的ITM测量建立时间。应适当增加“Timing”(定时)菜单中的“#Samples”,以确保稳定后的读数显示在图形中。在测量小电流时,采用“Quiet Speed Mode”或在“Timing”菜单中增加额外滤波。请注意,这是噪声和速度之间的平衡。滤波和延迟越大,噪声越小,但是测量速度也越小。

V电磁干扰和屏蔽

当带电物体接近被测电路时,会发生静电耦合或干扰。低阻抗时,由于电荷消失很快,所以干扰的影响不明显。然而,高电阻材料不会使电荷快速衰减,则会造成测量不稳定、噪声很大。通常情况下,当被测电流≤1nA或者被测电阻≥1GΩ时,静电干扰就会成为问题。

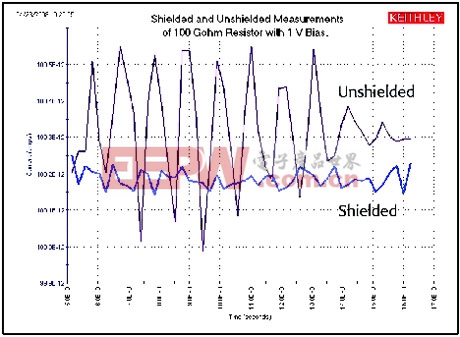

为了减小静电场影响,被测电路可被密封在一个静电屏内。图8所示为非屏蔽和屏蔽测量一个100GΩ电阻之间的巨大差异。非屏蔽测量比屏蔽测量时的噪声要大得多。

图8. 100GΩ电阻的屏蔽和非屏蔽测量的比较

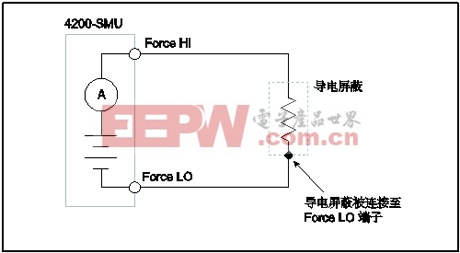

屏蔽可以仅仅是一个将测试电路包围起来的简单金属盒或金属网。商业探针台往往将敏感电路密封在一个静电屏蔽内。屏蔽被连接至测量电路LO端子,该端子不一定接地。对于4200-SCS来说,屏蔽连接至Force LO端子,如图9所示。

图9. 屏蔽高阻器件

采取以下步骤将静电耦合导致误的差电流降至最小:

•屏蔽DUT,并将屏蔽层在电气上连接至测试电路公共端——4200-SCS的Force LO端子。

•使所有带电物体(包括人员)和导体远离电路的敏感区域。

•测试区域附近避免移动和振动。

VI漏流和保护I

漏流是施加电压时通过(泄露)电阻的误差电流。当DUT的阻抗与测试电路中绝缘体的阻抗相当时,该误差电流就会成为问题。为减小漏流,在测试电流中采用高质量的绝缘体、降低测试实验室的湿度,并采用保护。

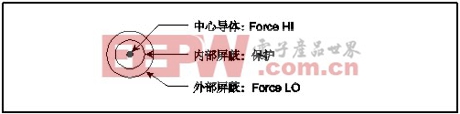

保护是由一个低阻源驱动的导体,其输出为或接近高阻端子的电势。保护端子用于保护测试夹具和电缆绝缘电阻和电容。保护是三轴连接器/电缆的芯屏蔽,如图10所示。

图10. 4200三轴连接器/电缆的导体

请勿混淆保护和屏蔽。屏蔽通常意味着采用金属护栏防止静电干扰影响高阻电路。保护则意味着使用增加的低阻导体,将其维持在于高阻电路相同的电势,它将拦截任何干扰电压或电流。保护不一定提供屏蔽。下图

为保护的两个例子:1)利用保护降低测试夹具导致的漏流,而2)则利用保护降低由于电缆连接产生的漏流。

图11所示为保护消除可能会通过测试夹具内隔离绝缘体的原理。在图11a中,漏流(IL)通过隔离绝缘体(RL)。该漏流增加至来自于DUT (IDUT),然后被SMU安培计测得(IM),对小电流测量的准确度造成不利影响。

- 正确选择和使用逻辑分析仪:逻辑分析仪原理(12-01)

- 准确测量脉冲信号的S参数(二)(11-12)

- 准确测量脉冲信号的S参数(三)(11-12)

- 变频群时延的测试(03-03)

- 低调制指数频偏测量方法(03-03)

- 网络分析仪测天线S参数应用实例(03-03)