基于MC8051内核的便携幅频特性测试仪设计

2.2 扫频信号源设计 3 系统软件设计 3.1 51内核的初始化配置

扫频信号源的性能指标直接影响仪器的测试精度,本文采用DDS技术产生扫频信号。这里有两条途径可供选择,一种是采用专用的DDS芯片,如AD9854等,利用FPGA发送频率控制字产生扫频信号;另一种是采用FPGA中集成的正弦查询表IP核,这是一种利用“IP核+D/A”相结合来实现DDS技术的方法,在充分提高FPGA内部资源利用率的前提下,又可以有效降低系统的硬件复杂度和成本,因此系统采用该方式。

设计环境使用Xilinx公司的ISE7.1,通过Core Generator生成正弦查询表IP Core,查询表中的波形数据存储在FPGA的块存储器(Block Memory)中。查询表IP核的输入相位控制字THETA与实际相位之间的关系为:

该频率精度完全达到设计要求。

2.3 系统接口模块

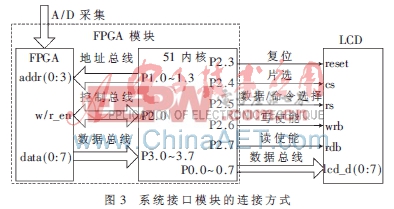

在该系统中,液晶模块采用ILI9320片上系统(SoC)驱动器[2],颜色显示深度为18位,分辨率为240RGB×320像素。系统采用i80总线结构控制液晶显示,即通过读使能(RDB)和写使能(WRB)两条控制线进行读写操作,数据线的宽度为8位。液晶模块中的控制信号和数据信号均为标准的TTL电平,可以直接与FPGA的I/O接口相连。

51内核具有8位总线宽度,通过内部端口映射的方式实现与FPGA模块的接口连接。为了实现FPGA采集数据的实时传输和显示,在接口设计中除了数据总线(data)以外,还需要地址总线(addr)和控制总线(w/r_en),按照程序设定的通信协议与FIFO中缓存的数据通信,实现数据传输和译码显示。系统接口模块的连接方式如图3所示。

系统软件设计主要完成对正弦查找表IP核的初始化、峰值检波程序的设计、异步FIFO设计、FPGA与异步FIFO的通信协议设计以及同步显示等问题。软件设计总体框图如图4所示。

51内核采用完全同步的设计方案,在统一的时钟信号下控制每一个存储单元的读写操作。根据51内核处理速度的要求,在设计中使用20 MHz的时钟,时钟信号通过系统总时钟分频得到。设计中,首先在Keil编程环境中编译C语言代码,该代码主要负责LCD的初始化并将FPGA采集得到的实时数据进行译码和显示。编译后生成的.hex文件经相应的格式转换,生成FPGA的ROM资源可加载的.coe文件类型。

通过Xilinx提供的Core Generator工具,对IP核使用的DATA、XDATA和CODE三种存储区进行初始化配置,存储区的大小设置要以C语言程序所消耗的存储资源以及FPGA内部Block Memory资源总的大小而定。本系统中所有存储区的数据宽度均设置为8位,其中各存储区对应的地址信号宽度为7位、11位和14位。将CODE区配置为只读模式(Read Only),用于存放51内核的指令代码,并载入已经生成的.coe文件。经综合、翻译、映射、布局布线和生成编程文件完成51内核的设计过程[3]。

在51内核中实现彩屏液晶的显示控制和数据译码显示,可以大大减小因彩屏初始化时序复杂和FPGA在人机交互界面设计中的不灵活性而带来的难度[4]。同时,采用C代码对液晶屏进行操作具有广泛的通用性和可扩展性,当LCD的型号改变时,只需对初始化控制字稍作修改就可以实现显示控制。

3.2 峰值检波模块

系统采用软件编程的方法实现峰值检波的功能。首先将扫频区间等分,逐个测量等分点处的信号峰值并将计算出的增益存入FIFO中,当一次扫描结束后就能获得系统的幅频特性数据。

在对信号最值电压进行测量之前,由于信号很容易受到干扰,所以不排除信号会发生抖动的可能。基于这个原因,在测量前采用简易滤波对信号进行平滑处理,以减少最值测量的误差。这里采用取均值的方法。对输入信号依次取值、保存,形成一个新的信号,该信号电压由原输入信号的前两个时钟所得电压和后两个时钟所得电压之和取均值得到。对信号进行简易平滑处理后,所产生的新信号作为最值测量的基准信号。信号整形后得到标准的方波信号,该信号的一个周期刚好对应输入信号的两个周期,其中高电平和低电平各对应一个周期。

信号电压的峰峰值即为最大值减去最小值。但是,信号经过A/D转换器量化以后,所得到的值为12位偏码,扩展成为16位偏码,“1111111111111111”表示电压为2 V,“1000000000000000”表示电压为0 V,“0000000000000000”表示电压为-2 V。如果直接将最大值和最小值的偏码相减,结果会出现错误。因此采用先将最小值(电压负值)变为相应的电压正值的方法,即:

其中B表示最小值,A表示相应的电压正值,然后再将相应的电压正值与最大值相加,即为信号电压的峰峰值。

3.3 异步FIFO设计

A/D采集数据的数据率很高,本文中系统时钟为40 MHz,采集数据宽度为12位,这样每秒采集的数据量为40 M×12 bit/8=60 MB/s,如此高速的数据流远远超出了51内核的处理能力。为保证51内核读取数据的有效性和可靠性,系统中使用异步FIFO对数据进行缓存。FIFO的设计是通过配置FPGA内部的Block RAM资源实现的[5,6]。为了实现边采集边显示的目的,配置两块相同的FIFO,大小均为512×8 bit。在读写时钟的控制下,通过读使能和写使能信号的设置,使得在同一时刻始终有一块FIFO在进行写操作,而另一块FIFO将写满的数据读出。对于同一块FIFO不允许读写信号同时有效,这样接收和读取A/D数据并交给51内核处理可以同时进行,从而保证数据传输的连续性。

- 高速误码测试系统中的C8051F005运用(02-18)

- 基于C8051F040单片机的温度遥测遥控系统(05-28)

- 基于LabVIEW和C8051F350的纺丝张力监控系统(02-18)

- 基于8051单片机温度采集及无线发送(02-24)

- 基于C8051F020的示波器监控程序设计(08-22)

- 超声波回波衰溅理论浓度计设计(11-01)