应用于芯片测试平台的Virtex-6 GTX收发器设计

引言

在计算机和工业系统中,芯片与芯片经常需要进行高速的数据交换,而高速串行I/O迅速取代传统的并行I/O正成为业界的趋势。随着数据传输速率的提高,并行I/O接口面临着诸多挑战,如信号延时、接口数据的对齐、引脚过多以致PCB布线困难等。千兆位(Multi-Gigabit)串行I/O最主要的优势是速度,以本文使用的XC6VLX240T FPGA为例,其GTX单通道速率为600Mbps至6.6Gbps,单片FPGA具有20个GTX收发器,可以实现总带宽为200Gbps的输入和输出。此外,串行接口采用差分信号受噪声影响小,引脚数少从而简化PCB版图设计,具有更好的电磁兼容和更低的成本。目前除DDR内存外,其他计算机并行I/O基本被串行I/O接口取代,如表1所示。

WiGig(Wireless Gigabit,无线吉比特)联盟致力于在60GHz频段上实现7Gbps的超高速无线传输,基于IEEE 802.11ad和WiGig 1.1标准,实现家用高清视频的无线传输。基于Virtex-6 FPGA的芯片测试平台需实现协议适配层(PAL)功能,并完成FPGA与ASIC间数据流的实时传输。如果采用并行I/O接口实现7Gbps数据传输,ASIC芯片需要上百只引脚和高速时钟,这将给芯片以及PCB版图设计造成诸多困难,而采用2通道GTX收发器只需8个引脚即可实现10Gbps的数据传输。本文设计基于Virtex-6 FPGA和Aurora 8B/10B编解码的单通道GTX收发器,以验证该方案的可行性。

芯片测试平台搭建

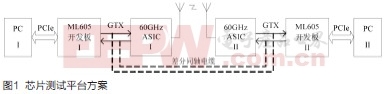

基于FPGA的芯片测试平台采用PC—FPGA—ASIC模式,实现方案如图1所示。PC端运行PCIe驱动程序,通过PCIe接口与FPGA通信,完成源文件的导入导出;GUI图形界面用于配置ASIC芯片并监视传输速率。Xilinx ML605开发板完成PCIe协议,通过IIC总线配置ASIC芯片;实现协议适配层(PAL)功能,将来自上位机的源文件转化为符合IEEE 802.11ad标准的数据流,并通过GTX收发器传输至60GHz ASIC芯片。ML605开发板的FMC HPC和LPC接口为测试平台子卡的设计留下足够的空间。如图1虚线所示,在接入ASIC芯片之前,测试平台应实现两片FPGA芯片之间的数据传输。

- 固定1024点流水线FFT处理器研究(07-28)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)