一种创新的晶圆级热载子并行测试方法

引言

随着VLSI集成度的日益提高,MOS器件尺寸不断缩小至亚微米乃至深亚微米,热载子效应已成为最严重的可靠性问题之一。现今,为了降低成本,减少周期,不断的提高工艺,晶圆级的器件可靠性测试愈来愈被广泛的应用。纵观许多晶圆级的器件可靠性测试,相对于其他器件可靠性测试项目如前端的TDDB、Vramp、Jramp及后端的恒温电迁移测试的测试时间,热载子效应测试需要花费的时间更长。当务之急是怎样缩短热载子效应测试周期。

为了缩短测试周期,有些公司采用对器件施加更高的HCI应力条件来加速器件的退化,但是这种方式并不看好,因为在更高的HCI应力条件下,器件的物理机制已发生了变化。在我们想要解决周期过长的问题前,我们先参考封装级的热载子效应测试。在封装级的热载子效应测试中,有一种测试板可以支持几个器件同时进行测试。如果我们仿照这种封装级的热载子效应测试,把它应用在晶圆级,那晶圆级的热载子效应测试周期将会大大的缩短。

基于这样的想法,我们提供了一种创新的、在原有的测试程序基础上编制的一套更复杂的并行测试程序,从而有效地缩短了晶圆级的热载子效应测试周期。而且数据表明,新旧方法的测试结果具有很好的可比性和一致性。

实验

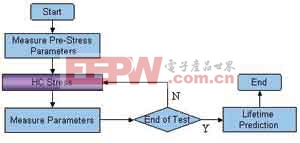

传统的晶圆级热载子效应测试程序(PDQ-WLR,版本3.01[2])是由美国Sandia Technologies inc.公司提供的,在Agilent 4072自动控制测试机台上完成测试。它的测试流程是用HCI_4_MOS_Builder生成两个设置文件,一个是参数施加命令文件,另一个是完成施加HCI应力条件的时间读点文件,并且按照图1所描述的测试流程来完成测试。由于商业要求,这套程序是被打包,不可改变的。

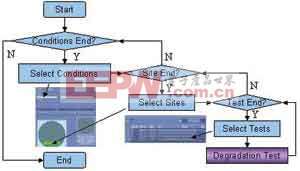

图1a 热载子效应测试总流程

图1b 热载子效应退化的应力施加及电性参数测试流程

传统的晶圆级热载子效应测试是一个器件一个器件的被施加HCI应力条件。测试的总时间是根据测试器件的个数,不同的HCI应力条件个数,以及不同HCI应力条件下实际应力施加的时间的总和来计算。例如,热载子效应测试有3种不同的HCI应力条件,每种HCI应力条件要有3个器件来做样本,每次要施加HCI应力条件10 000秒,再加上器件退化后所要测量的特性参数的时间,总的测试时间要花费大约27小时——27=3*3*(1000+10000)/3600)。这个时间是一种类型器件完成一次的时间,例如NMOS晶圆级热载子效应的测试时间,如果是几种不同类型的器件,相应的时间将是成倍的增加。从图1a(热载子测试的总流程),和图1b(热载子效应退化的应力施加及电性参数测试流程),我们很清楚的可以算出超过90%的时间是用在施加HCI应力条件使器件退化的时间上。所以我们开发了一套程序来实现对一组同样类型的器件进行并行施加HCI应力条件,以此取代传统的串联方式的一个器件一个器件施加HCI应力条件及参数测试的流程。

人们也曾试着改变版图的器件连接方式,例如将几个器件需要施加HCI应力条件的端口(栅极或漏极)连接在一起,这样一来,用传统的由美国Sandia Technologies inc.公司提供的程序也可以同时施加HCI应力条件在几个器件上。但由于从同一个施加HCI应力的端口到几个器件的连线长短不同造成的寄生电阻,使得一小部分HCI应力压降会损失在这些连线上,最终导致这几个器件实际被施加的HCI应力不一致,造成误差。图2a和图2b显示了在版图上改变器件的连接方式。

阅读全文请点击下载PDF和在线阅读>>

http://www.epc.com.cn/free_test/index_new.htm

- 可以处理6.4Gbps以上数据率的创新型串行总线测试方(06-29)

- 通过创新图形化开发平台快速构建移动机器人的原型(12-11)

- 用于多站点并行测试的 ACS集成测试系统(02-27)

- 浅谈综合布线测试仪的测试方法与标准(05-17)

- 气密封性测量装置(06-21)

- 基于模板元编程的量纲检测方法(09-18)