PCIE 3.0的动态均衡测试挑战

一、PCIE 3.0中使用的动态均衡概念

因为PCIE 3.0信号的速率可以达到8Gb/s,而且链路通道走线也可能会很长,这可能会导致高速信号衰减过大,在接收端无法得到张开的眼图。因此在PCIE 3.0的Tx和Rx端均使用了均衡设置,以补偿长链路时高速信号的衰减。

但由于实际产品中PCIE 3.0信号的传输链路的长度是不一致的,有时候长,有时候短,此时可能只需要Tx发送端的均衡即可实现良好的补偿,而不需要Rx端的均衡;或者在Tx发送端与Rx接收端使用相应的均衡等级组合才可能得到最优的眼图。而Tx端有11级Preset均衡设置,Rx端也有具有行为特性(即相关的参数设置会随着情况的不同而不同)的CTLE、DFE等多种均衡算法和设置以及CDR时钟恢复,这使得针对不同的链路情况设置不同的均衡设置变得更加复杂。

PCIE 3.0中使用了动态均衡(Dynamic Equalization)的方法来自动实现和配置得到最优的均衡组合以满足不同时候的需要。即系统会自动根据链路的情况分析高速信号在接收端的性能(眼图等),通过分析结果来指导Tx发送端和Rx接收端如何设置均衡参数。如下图所示,在PCIE 3.0的发送端和接收端器件工作初始化过程中,系统会根据对链路的分析情况,要求Rx接收端发送TxEQ Preset设置请求给Tx发送端要求其进行相应的Preset均衡设置,Tx发送端也会发送RxEQ均衡设置请求给接收端要求其进行相应的RxEQ设置,通过这样一个初始化过程获得一个最优的均衡设置,从而在接收端得到最优化的高速信号(眼图)。

PCIE 3.0的动态均衡初始化过程包括如下4个阶段:

Phase 0:下行端口使用8b/10b编码方式传达发送端和接收端预设值(preset)给上行端口,这些值使用TS2(Train Sequence2)训练序列来传达。当信号速率切换到8GT/s以后,上行端口发出包含有其收到的预设(Preset)值的TS1训练序列。

Phase 1:通过交流TS1序列,带有预设(Preset)的8GT/s初始化链接成功(BER=10e-4)。

Phase 2:下行端口器件通过TS1训练序列发送均衡请求来调整上行端口器件的输出设置,直到获得最优设置为止(BER=10e-12)。

Phase 3:上行端口器件通过TS1训练序列发送均衡(均衡系数/预设)请求来调整下行端口器件的输出设置,直到获得最优设置为止(BER=10e-12)。

二、PCIE 3.0中使用的动态均衡的优缺点

PCIE 3.0中使用动态均衡方法能够针对不同的情形自动配置并优化发送端和接收端的均衡设置,补偿信号的传输通道对高速信号带来的影响(如损耗),以在接收端获得最好的信号质量。

但是动态均衡优化过程需要花费时间,有时候可能会导致系统工作或运行超时等错误。因此,PCI Express® Architecture PHY Test Specification Revision 3.0 规范的2.3, 2.4, 2.7, 2.10 及2.11等章节规定了对动态均衡链接(link equalization)的测试,规定动态均衡链接需要在特定的时间内(小于500ns)完成。

三、PCIE 3.0中动态均衡的测试挑战

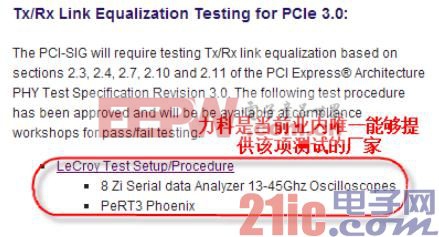

由于动态均衡测试需要测试仪器能够具有协议能力,即仪器可以与被测件进行协议握手通信。当前很多测试方案中的误码仪都不具备协议能力。只有力科公司(Teledyne LeCroy)的PeRT3 Phoenix具有基于PCIE 3.0的协议通信能力。因此,目前只有力科公司(Teledyne LeCroy)能够实现规范要求的这项测试,也是PCI-SIG协会推荐的测试方法,如下图所示为摘自PCI-SIG协会网站上对于PCIE 3.0的Tx/Rx Link Equalization测试项目所推荐的测试设备:

四、力科针对PCIE 3.0的Tx/Rx Link Equalization测试方案

1、Tx Link Equalization测试

(1)测试设备:PeRT3 Phoenix(具有协议使能的接收端发送端容限测试仪)及示波器SDA8Zi

(2)测试目的:被测件的Tx端是否能够应答协议级别的均衡预设请求,是否能够在规定的时间内完成响应。

(3)测试连接示意图如下:

如图中所描述,示波器将配合自带的测量参数和力科示波器独有的基于PCIE 3.0的协议分析软件(Protosync协议分析软件)实现Tx Link Equalization的测量。

2、Rx Link Equalization测试

(1)测试设备:PeRT3 Phoenix(具有协议使能的接收端发送端容限测试仪)

(2)测试目的:被测件的Rx端是否能够应答协议级别的均衡预设请求,是否能够在规定的时间内完成响应。

(3)测试连接示意图如下:

安装相关步骤完成设置,能够进入loopback 进行误码测试,即表示Rx Link Equalization 测试满足要求。具体步骤请参考:LeCroy_CEM3_0_Link_EQ_Test_Procedure_v0_9pdf。

- 高速串行数据链路的自动化一致性测试(04-15)

- 基于示波器的高速的全方位分析实现(06-12)

- PCIE 3.0的发射机物理层测试——力科PCIE 3.0系列之一(11-10)

- PXI技术最新发展与应用(01-23)

- PCIE 3.0的动态均衡测试挑战——力科PCIE 3.0系列文章之二(11-10)

- 致远电子:高精度功率分析仪是如何炼成的?(03-16)