A/D转换器的保真度测试检验纯度

引言

对正弦波进行精确数字化的能力是高分辨率A/D转换器保真度的一项敏感度测试。该测试需要一个具接近1ppm残留失真分量的正弦波发生器。此外,还需要一个基于计算机的A/D输出监视器,用于读取和显示转换器输出频谱成分。若想以合理的成本和复杂程度来实施此项测试,就必需进行其元件的设计并在使用之前完成性能验证。

概要

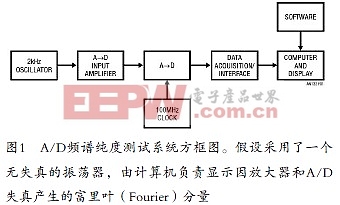

图1给出了系统的示意图。一个低失真振荡器通过一个放大器来驱动A/D。A/D输出接口对转换器输出进行格式化,并与负责执行频谱分析软件和显示结果数据的计算机进行通信。

振荡器电路

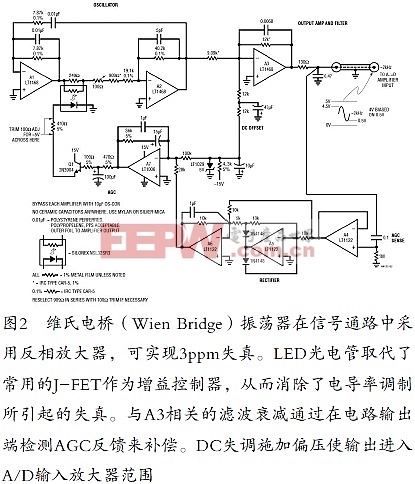

振荡器是系统中难度最大的电路设计部分。为了对18位A/D进行有意义的测试,振荡器的不纯度必须超低,而且这些特性必须采用独立的方法加以验证。图2基本上是一款“全反相”2kHz维氏(Wien)电桥设计(A1-A2),其在哈佛大学Winfield Hill所做研究工作的基础上进行。原始设计的J-FET增益控制被一个LED驱动的CdS光电管隔离器所替代,从而消除了由J-FET电导率调制引起的误差,同时也就不必为最大限度地减少这些误差而进行微调。限带的A3负责接收A2输出和DC失调偏置,并通过一个2.6kHz滤波器提供输出以驱动A/D输入放大器。用于A1-A2振荡器的自动增益控制(AGC)信号由负责给整流器A5-A6馈电的AC耦合A4从电路输出(“AGC检测”)获取。A6的DC输出表示电路输出正弦波的AC幅度。利用终接至AGC放大器A7的电流求和电阻器来使该数值与LT1029基准保持平衡。驱动Q1的A7通过设定LED电流(因而还包括CdS光电管电阻)来闭合增益控制环路,从而稳定振荡器输出的幅度。尽管这会衰减A3和输出滤波器的带限响应,但从电路的输出获得增益控制反馈信息可保持输出幅度。另外,它还对A7环路闭合动态特性提出了要求。确切地说,A3的频带限制与输出滤波器A6的滞后及纹波抑制组件(在Q1的基极中)相组合,可产生显著的相位延迟。A7上的一个1μF主极点和一个RC零点一起提供了该延迟,从而实现了稳定的环路补偿。这种方法用简单的RC滚降滤波器取代了严密调谐的高阶输出滤波器,从而在保持输出幅度的同时最大限度地降低了失真。

- DDS函数信号发生器的优点(09-28)

- 低失真、覆盖三个十倍频程的锁定同步正弦波发生器(11-02)

- 混合集成特定频率信号发生器的设计(11-30)

- 新颖的网线自动检测装置(02-02)

- 时钟的抖动测量与分析(03-16)

- EMI的来源及干扰后果(07-17)