基于物联网的智能楼宇变形沉降监测系统

存、一个内置10/100以太网媒体接入控制器(MAC)、一个具有OTG(on-the-go)功能的全速(12Mbps) USB 2.0接口,以及一个SRAM/SDRAM外部总线接口。是Atmel宣布推出的业界最低功耗的32位闪存微控制器系列。

主控制器芯片AT32UC3A0512能够以66MHz的速率提供80 Dhrystone MIPS(DMIPS)的性能,而在3.3伏电压下的电流仅为40毫安。此外,其功耗低至1.65mW/DMIPS,只是具备相同功能的其它架构的1/4,表现远远优于对手。这款新的微控制器专为联网和以个人电脑为中心的嵌入式应用产品而开发,尤其适合于便携式设备。

AVR32 UC内核采用了三级管线型Harvard架构,该架构主要为优化片上闪存的指令存取而设计。此外,它也是业内首个让单周期读写SRAM绕过系统总线而直接与CPU介接的内核,从而实现更快的执行速度和周期决定过程,以及更低的功耗。AVR32 UC内核与其前身AVR32 AP共享相同的指令集架构(ISA),其中有220多条无方式指令 (modeless instruction) 可作为16位压缩指令和32位扩展指令使用。该ISA架构拥有独立位(atomic bit)的处理功能,可控制片上外围设备和通用输入输出(IO) ,以及定点DSP计算,如单循环小数饱和乘法及累积算法。另外,该内核还含有一个事件处理系统,可以支持优先中断、不可屏蔽中断及内部异常等事件,其中断反应时间最长为16个时钟周期。

AVR32 UC3A系列集成了许多与爱特梅尔 ARM 微控制器相同的外围设备,包括外围DMA控制器、多层高速总线架构、10位模数转换器 (ADC)、2个串行外围接口(SPI)、同步串行接口 (SSC)、双线接口 (I2C兼容)、4个通用异步收发器 (UART)、3个通用计时器、7个脉宽调制器以及一整套监控功能。

10/100Mbps IEEE 802.3 标准以太网 (MAC) 能让开发人员设计出可以通过互联网协议堆进行通信的联网嵌入式系统。USB 2.0全速 (12Mbps) 接口提供了利用各种 USB 级别接口 (例如针对串行数据通信的人机接口设备;或针对更大规模数据传输的大容量存储器) 与现今的 PC 架构通信的方法。由于UC3A USB外设的OTG功能提供对USB闪存盘、指针设备或打印机等标准USB设备的支持,因此让以PC为中心的计算环境得以进一步集成。

外部总线接口(EBI) 将可寻址(addressable)的物理存储器扩大到16MB。其非复用的16位数据总线能够与高密度的外部SRAM、SDRAM、ROM、闪存器件以及如LCD或FPGA等存储映像器件连接。

UC3A系列微控制器拥有一个6层高速总线矩阵,该结构使总线主外设能够以66MHz每秒264MB的最高速度同时访问任何总线从设备。这些总线主控设备(master)包括AVR32 UC核数据和指令接口、15信道外围DMA控制器,以及几种高速外围设备,如以太网MAC和USB。总线从设备(slave)则为片上SRAM和闪存、USB、2个外围总线桥,以及外部总线接口。

配套资源配置:爱特梅尔免费为UC3A系列产品提供GNU gcc C编译器、GNU gdb调试器、FreeRTOS.org实时内核和 lwIP TCP/IP 协议堆栈。此外,还提供IAR (Embedded Workbench)、ExpressLogic (ThreadX) 以及 Micrium (uCOS/II) 的商用许可。爱特梅尔的 AVR32 Studio 和 AVR JTAGICE mkII 为 AVR32 UC 提供了一个多平台集成开发环境 (IDE),已针对GNU工具链进行配置,其中包括对更先进的调试法 (如实时追踪) 的支持。EVK1100评估套件则提供以太网和USB接口,以及诸多其它串行通信接口,如SPI、TWI与USART。另外,爱特梅尔更提供20x4字符点阵的LCD与扩展连接器,可支持高端产品评估与原型开发活动。

EVK1100开发板配备了一系列丰富的外设、内存,并且可充分开发AVR32设备的全部潜能。 包括以下外设:

★以太网端口

★传感器:光照、温度、电位器

★4x20蓝色LCD(PWM变频背光)

★JTAG连接器、Nexus、USART、USB 2.0接口,TWI接口、SPI。

★SD和MMC读卡器

3.3 系统软件架构

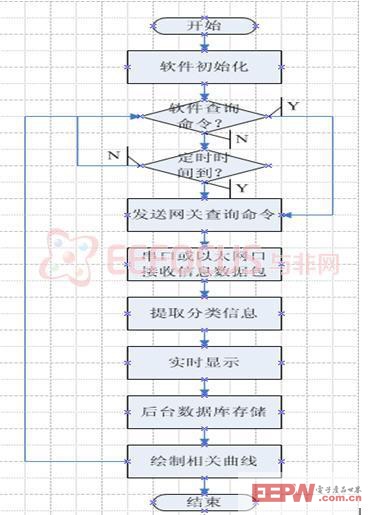

系统软件拟基于VC++6.0开发设计,数据库可选简单的ACCESS数据库或成熟的SQL SERVER数据库开发设计。上位机控制程序配备后台数据库,可存储一定时间内的各楼宇的历史变形沉降信息,经程序分析处理后绘制成人性化的曲线展现给用户,当然用户也可发送命令随时查看楼宇某时间的变形沉降情况。上位机控制程序可通过计算机的串口对直连的嵌入式网关模块进行控制,也可以通过Internet网络TCP的网络协议对远程嵌入式网关进行控制。

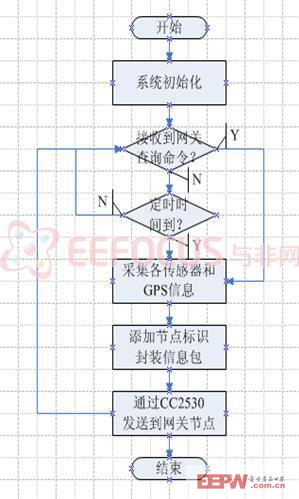

4 系统软件流程

上位机控制程序软件流程图如图5所示,嵌入式网关节点程序流程图如图6所示,信息采集节点程序流程图如图7所示。

图5

图6

图7

3.4 系统预计实现结果

目前实际应用的楼宇变形沉降监测系统绝大部分都是基于GPS的简单系统,功能不够完善,具有很多缺点,所

智能楼宇 变形沉降监测 物联网 无线传感器网络 CC2530 AT32UC3A0512 相关文章:

- Cortex-M3的生态物联网数据采集分站设计(10-11)

- 基于物联网技术的智慧汽车检测线解决方案(04-07)

- 适合嵌入式射频系统调测的混合域示波器(06-13)

- 泰克MDO4000混合域示波器应用案例分析四——RF模块功能验证及调试(07-30)

- μTrace对Cortex-M处理器进行智能调试与跟踪(12-16)

- 盘点NI 2014年关键技术,看软硬件平台如何推动工程创新(01-13)