FinFET对动态功耗的影响

现在主要的代工厂都在生产FinFET晶体管,这些FinFET以创纪录的速度实现了从设计到现货产品的转变。FinFET的发展普及一直都比较稳定,因为与平面器件相比,它们可以提供更低的功耗、更高的性能和更小的面积。这使得FinFET对智能手机、平板电脑及要求长电池寿命和高性能的其他产品来说极具吸引力。

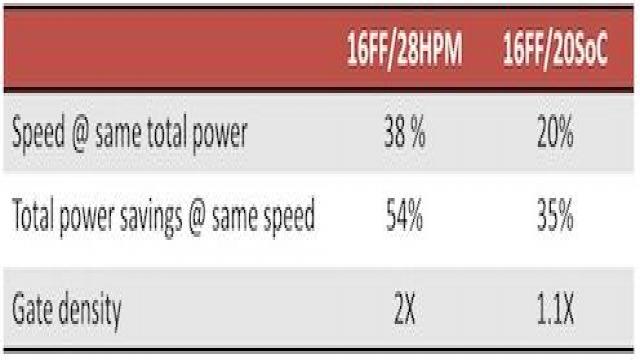

当 Intel首次在22nm节点使用FinFET时,他们声称与bulk、PDSOI或FDSOI相比,FinFET在相同的总功耗条件下性能高出37%, 或者在相同速度条件下功耗低50%。这些数据非常有吸引力,而且在向14nm及更小工艺节点发展时还有进一步改进的空间。

图1. FinFET的性能,功耗和面积优势(来源:TSMC. Presented at Open Innovation Platform 2014)

在 使用功耗方面,控制功率泄漏对于平面器件,特别是在较小的节点来说,已然成为了一项艰巨挑战。通过抬升沟道,包裹沟道四周的栅极,FinFET可以创建一 种完全耗尽型沟道,从而克服平面晶体管的漏电流问题。FinFET所具有的更好的沟道控制能力可以用来实现更低的阈值和供电电压。

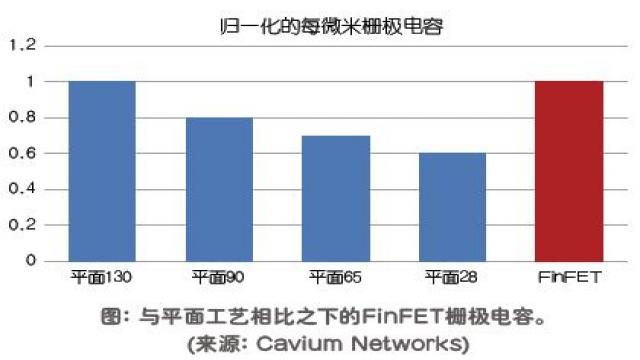

虽然漏电流在FinFET中是受控的,但动态功耗占总功耗的很大部分。与平面晶体管相比,FinFET具有更大的引脚电容,因而会导致更高的动态功耗值。据CaviumNetworks描述,"与28nm工艺相比,FinFET的每微米栅极电容提高了66%,与130nm平面节点的水平相当。"平面器件和FinFET器件的栅极电容值比较如图所示。

图2:与平面工艺相比之下的FinFET栅极电容。

那么这对设计工程师来说意味着什么呢?从实现角度看又会对设计流程造成怎样的改变?动态功耗(也称为开关功耗)在优化过程中应成为一个代价函数,必须在流程的所有阶段加以充分考虑。

FinFET 增加了物理设计流程的复杂性。更严格的设计规则和FinFET工艺要求(比如具有电压阈值意识的间距设计、植入层规则等),都将对综合、布局、底层规划和 优化引擎施加约束,从而直接影响设计的指标。同时由于FinFET是在16nm/14nm工艺实现,多重图案技术将自动成为使用FinFET的任何设计的 一部分,这又增加了另一层的复杂性。

针对FinFET的设计自动化技术需要具有FinFET意识,以降低开关功耗,并提供具 有功耗意识的RTL综合、活动驱动型布局和优化、时钟树综合(CTS)功耗降低以及并行优化动态与泄漏等功能。功耗优化需要从设计流程的早期开始,架构选 择需要具有功耗友好特性,以便确保设计在实现时具有最低的功耗。

数字实现过程是从RTL综合开始的。由于FinFET被应用于最新、最大的设计,RTL综合引擎必须拥有在合理运行时间处理1亿个以上门电路的 能力。当然,它还必须提供高质量的结果,这可以在考虑芯片的所有因素后在全芯片级执行RTL综合来实现。执行多个具有不同设计约束条件的综合任务来探索不 同设计方案也是很有用的。能够观察设计指标如何相互影响有助于在满足功耗、性能和面积指标要求方面做出聪明的折中方案。

为了 满足功耗目标,实现流程需要从综合开始并贯穿整个物理设计流程,采取一系列的降功耗策略。最常见的策略包括多阈值库、时钟选通、多角落/多模式 (MCMM)功耗优化、引脚交换、寄存器集中、重映射和功率密度驱动型布局。RTL级功耗分析对于分析和修复设计流程早期出现的功耗问题来说非常重要。

在RTL和版图之间交叉检测的能力也有助于在设计流程早期识别和调试问题,并最大限度地减小最后一刻才发现问题的概率。

在先进节点使用FinFET的设计实现工具必须在与各家代工厂的紧密合作下得到增强和更新。在代工厂、EDA公司和双方客户之间要开展大量的工程技术合作,以便芯片设计人员能够充分发挥每种新工艺节点的优势。

- 扩展低功耗RF设备通信距离(09-26)

- 低功耗射频无线技术的发展(05-16)

- 低功耗蓝牙与专有射频技术在HID的应用概述(10-06)

- FPGA的低功耗设计(07-06)

- UHF RFID系统测试的挑战(04-20)

- 芯片厂竞相出招手机AP/显示器功耗大减(06-03)