10G-32G数字系统信号完整性测量技术白皮书

示波器

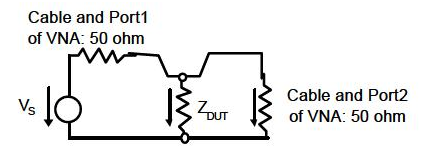

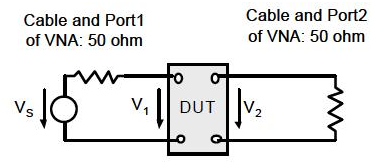

图7. 用双端口方法测试PDN输出阻抗

图8.

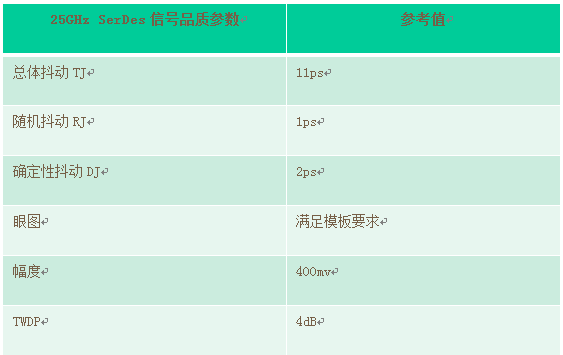

10GHz以上SerDes信号品质测量

表/图9. SerDes 典型信号品质参数要求

图10. 抖动成分关系图

确定抖动DJ是可以重复的、可以预测的定时抖动。正因如此,这个抖动的峰到峰值具有上下限,在数量相对较少的观察基础上,通常可以以高置信度观察或预测其边界。DDJ和PJ根据抖动特点和根本成因进一步细分了这类抖动。影响确定性抖动的关键因素是互连通道的损耗,损耗产生码间干扰抖动ISI。对于损耗可以用预加重和均衡的办法处理。

总体抖动TJ是随机抖动RJ和确定性抖动DJ的卷积关系。对于高速SerDes和高速数字系统,抖动都是第一重要参数,有时眼图不满足要求,系统仍然正常,但是抖动不满足要求,一般都会出问题。

数字信号的眼图包含丰富的信息,体现数字信号的整体特征,能够很好的评估数字信号的整体品质。对于高速SerDes信号,时钟是内嵌的,这时候需要仪器从串行信号中恢复时钟,以恢复的时钟为基准来形成眼图,如图11所示。现代的宽带示波器一般提供多种时钟恢复方式供选择,测试高速SerDes信号最常用的是Golden PLL方法,要根据具体规范的CDR响应曲线选择一级或二级锁相环,仔细设置时钟恢复参数。

图11. 高速SerDes信号眼图的形成

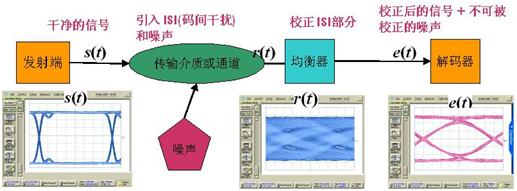

图12. 高速串行信号传输中的均衡

表/图13. 90000Q和86100D典型性能指标

工业标准

10G-32G数字系统信号完整性测量技 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)