使用OriginLab进行PMT能谱分析

首先介绍ADC的调试(ADC子板还要经过设计者的硬件等测试),对于SEP来说ADC的调试就是确认FPGA接收从ADC来的采样值是否正确。所以ADC采集PMT的信号并转换成数字信号送到FPGA,通过Virtual JTAG调试工具又从FPGA逻辑内读取ADC采样值进行离线分析。

读取ADC采样值时Virtual JTAG工具的使用方法介绍,对应的Quartus II工程名称是SEP_ES_debug,此时Virtual JTAG逻辑借用了TDC调试中用到的两个FIFO,即一个FIFO用于存储ADC采样值,另一个FIFO用于存储ADC采样值的积分值。所以在读取ADC采样值时,首先要往第一个FIFO里写入ADC采样值,使能信号通过按钮“FIFO Push CMD”发送,发送同时将滑动条设置为“1”(此时相当于给这个FIFO一个写使能信号),如果要停止写这个FIFO,那么就再次按这个按钮的同时将滑动条的设置为“0”(清除写使能)。读FIFO的时候点击按钮“Full Read FIFO”的同时在“Par1”输入窗口里设置读取的数目(注意此时Slider也需要同时设置为0)。(笔者注:Virtual JTAG调试平台参考其他文章)

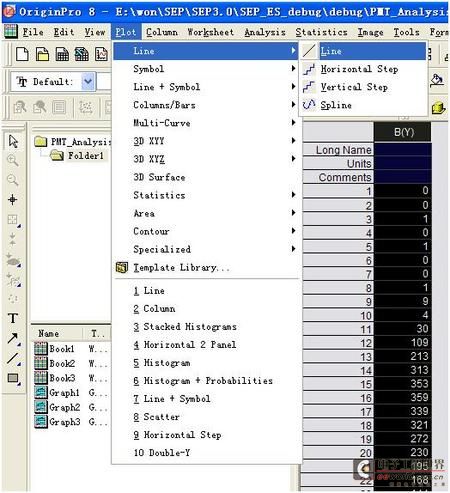

在OriginPro里分析ADC采样值,新建一个WorkBook,将读取到的ADC采样值拷贝到book中(新建的book默认有两列,即A列和B列,必须先删除一列),选择整列数据后使用Plot下Line命令(如图1所示)重建信号,如图2所示。

图1:在OriginPro中分析ADC采样值

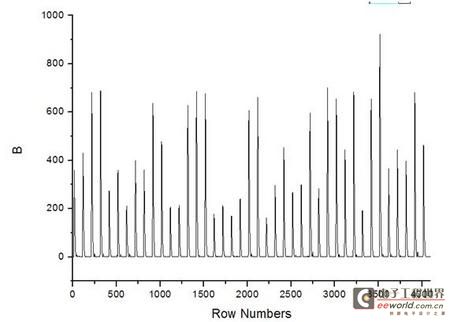

图2:重建后的ADC信号

注意图2重建后的ADC信号,是通过PMT脉冲产生的另外一个trigger信号触发FPGA逻辑锁存100个samples并存往FIFO。所以,在图2中看出的效果是各个脉冲之间间隔一致。

下面介绍PMT能谱测试,能谱测试的原始数据是ADC采样值的积分,存储在Virtual JTAG逻辑的第二个FIFO中。点击按钮“FIFO Push CMD”的同时将滑动条设置为“3”来使能逻辑向FIFO里写入积分值,如果要停止写这个FIFO,那么就再次按这个按钮的同时将滑动条的设置为“2”。读FIFO的时候点击按钮“Full Read FIFO”(注意此时Slider要设置为非0),这时不需要在“Par1”输入窗口里设置读取的数目,因为在Tcl代码里已经写死了,如果需要修改读取的数目,可以在tcl代码里直接修改。

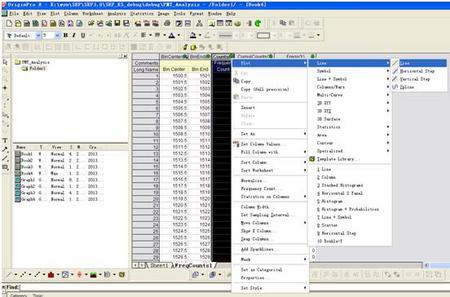

在OriginPro里分析PMT能谱,新建一个WorkBook,将读取到的ADC积分值拷贝到book中,选择整列数据并且右击鼠标,对数据进行“Frequency Count…”分析,如图3所示。结果会在本Book中得到另外一页分析后的数据(如图4所示),选择“Frequency Count”列数据并执行Plot下Line命令即可得到能谱分析结果(如图5所示)。

图3:首先分析ADC积分值

图4:执行命令得到PMT能谱分析结果

图5:能谱分析结果

OriginLabPMT能谱分 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)