信号完整性分析基础系列之三--串行数据测试中的CDR

时间:01-12

来源:互联网

点击:

在当今的GHz速率的串行数据测试中,眼图和抖动测试是最重要的两个测试项目。眼图和抖动测量中,测试仪器必须从待测试信号中恢复参考时钟,用该时钟同步和采样数据。因此,恢复时钟的方法会直接影响眼图和抖动测试结果,各种串行数据标准都规定了抖动测量中时钟恢复电路CDR的参数,正确的设置测试仪器的CDR参数才可以使测量结果与芯片接收端的实际性能保持一致。

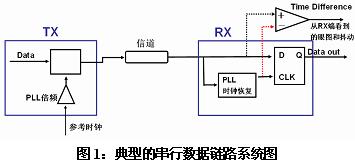

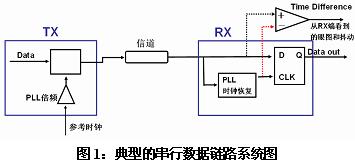

下图1所示为某串行数据链接的系统图,在Fibre Channel、Gigabit Ethernet、SDH等串行链路中都采用了这样的架构。发送端(TX)发送的信号通过信道传输到接收端(RX)后,收发器芯片RX部分的时钟恢复电路从串行数据中恢复出时钟,用恢复的时钟来同步串行数据,进行采样。由于多种原因,进入RX的串行数据信号可能有较大的抖动,理想情况下(锁相环PLL的环路带宽无穷大时),时钟恢复电路的PLL输出的时钟和RX的输入数据信号同相,即零抖动,这时,RX的判别电路(如图1中的D触发器)有最大的建立时间和保持时间余量。但是,由于PLL的环路响应为低通滤波器特性,只能消除串行数据中低频段的抖动,不能处理高频抖动,所以,现实情况中收发器芯片RX端“看到”的眼图是有抖动的。

在图1中,RX端PLL的参数是影响眼图和抖动性能的决定因素。PLL是一种广泛使用的电子电路,可以用于获得特定频率的时钟、射频信号调制与解调和串行数据的时钟恢复。

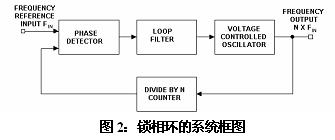

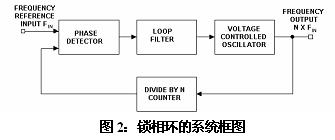

如图2为PLL的系统图,包括鉴相器(phase detector)、环路滤波器(loop filter)、压控振荡器(voltage controlled oscillator,简称VCO)三个基本部分。PLL的工作原理请参考模拟电路书籍。

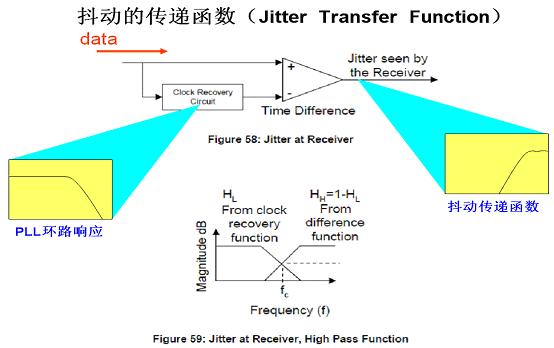

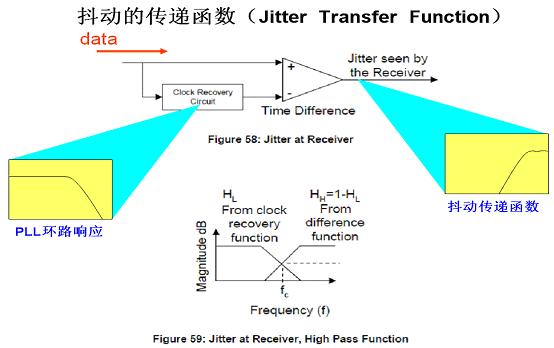

在接收端的PLL中,鉴相器、环路滤波器和VCO三部分组成的环路的频响为低通滤波器特性。如下图3所示,接收端的时钟恢复电路的频响是一个低通滤波器,其传递函数为HL,当串行数据信号的抖动变化频率较低时,即从直流到PLL的截至频率,PLL能及时追踪到数据跳变沿(即锁住相位),输出的时钟与输入数据同相(严格讲相位差为固定常数),这样抖动为零。当连续边沿的抖动变化太快时(即存在高频抖动时),PLL不能及时追踪到边沿的变化,于是输出的时钟和数据边沿存在抖动,所以,接收端的CDR不能滤除高于截至频率的抖动,它的抖动传递函数(Jitter Transfer Function简称JTF)的频响为高通滤波特性,接收端CDR又称为TIE抖动的高通滤波器。如图3,抖动传递函数HH=1-HL。

图3:抖动的传递函数

在收发器接收端除了采用如图1所示的PLL来恢复时钟外,另一种时钟恢复方法是使用相位内插器(phase interpolator,简称PI),在FBDIMM和PCI Express中都使用PI来恢复时钟,但是使用仪器测试时,可以用PLL来建模。

测试高速串行数据信号的眼图与抖动的仪器都使用了基于锁相环的时钟恢复方法。其中,实时示波器主要使用软件PLL来恢复参考时钟,取样示波器和误码率测试仪都使用硬件PLL来恢复时钟。实时示波器作为最普及和广泛应用的测试仪器,本文仅介绍实时示波器的软件CDR和眼图测试、抖动测试的关系。

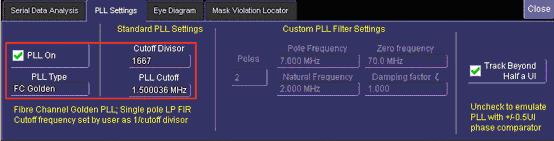

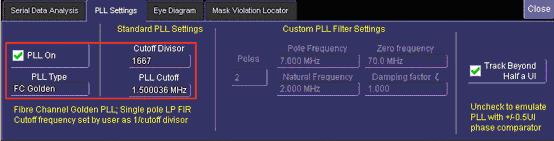

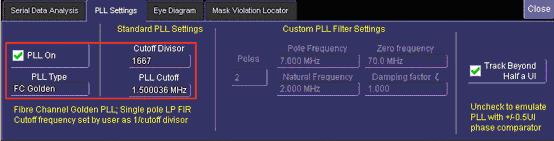

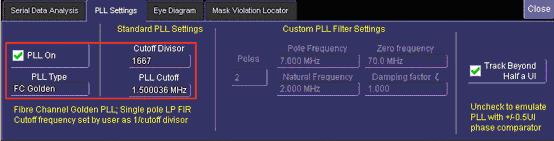

如下图4所示为力科串行数据分析仪中PLL设置的参考,缺省情况下使用FC Golden PLL,该PLL为1阶锁相环,其环路带宽等于比特率除以1667,最早是在Fibre Channel的MJSQ文档中定义的。

图4:力科串行数据分析仪的软件CDR设置界面

如下图5为使用力科示波器测量某2.5Gbps信号,当示波器的串行数据分析软件的PLL带宽在2MHz、5MHz、10MHz、20MHz四种设置下的眼图测量结果,可见,PLL带宽越高,眼图越清晰,抖动越小。问题是,待测试电路的收发器RX端接收到的、真实的眼图和抖动是什么样呢?答案是必须把示波器的CDR参数设置得和待测试电路RX端的CDR参数完全一致,这样示波器的测量结果才具备参考价值。

图5:示波器在不同PLL设置时测量同一信号的眼图

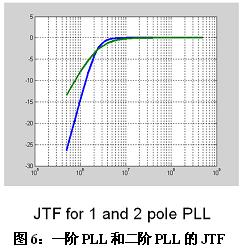

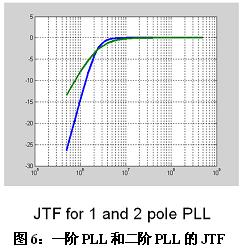

在图4和图5中都是一阶锁相环的CDR,在很多的串行电路标准中都使用这类PLL,比如GBE、XAUI、SDH、CPRI、FC、SAS等等。不过,PCIe Gen2、SATA2、Displayport则使用了二阶锁相环的CDR,如图6所示为一阶PLL和二阶PLL的JTF对比,二阶PLL有更加陡峭的滚降系数-40dB/decade(一阶PLL的滚降系数为20dB/decade)。假设某500kHz的抖动为150ps(而且500kHz在斜线的频段内),通过一阶PLL后抖动只有15ps,而通过二阶PLL后仅为1.5ps。可见,对于图6中低频段的抖动,二阶PLL可以更大幅度的降低该频段的抖动。

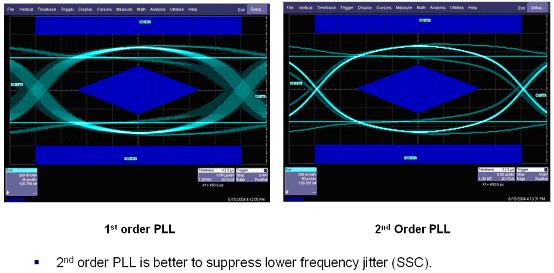

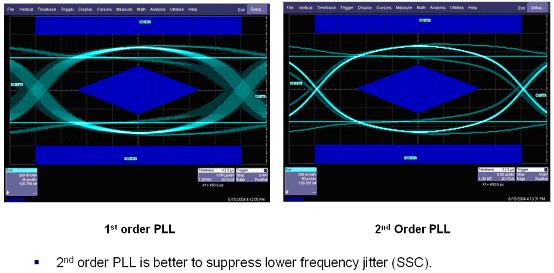

图7所示为某2.5Gbps信号,CDR使用一阶PLL或二阶PLL的眼图测量结果,可见,使用二阶PLL得到的眼图非常清晰、抖动更小。二阶PLL可以更大程度的减小低频抖动,通常用于带有扩频时钟(SSC)的串行数据信号,比如计算机主板上的SATA和PCIe。

图7:示波器在不同PLL设置时测量同一信号的眼图

如下图8所示,在力科SDA中,集成了FC Golden, PCIe Gen1, PCIe Gen2, DVI, FBDIMM, USB3.0和Custom多种PLL参数设置,测量时根据待测试信号的类型选择合适的CDR设置。

图8:力科示波器集成了多种PLL设置

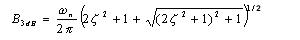

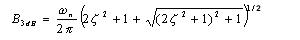

在Custom自定义锁相环模式下,可以选择1阶PLL还是2阶PLL。如果是自定义的1阶PLL需要设置极点和零点的频率,PLL的截至频率就是极点频率,零点频率必须高于前者,其决定了阻带的衰减系数;如果是自定义2阶PLL需要设置Natural Frequency(ωn)和Dampling factor(ζ),如图8红色标记所示,该PLL的环路响应的传递函数为H(s)(图8中黄色字体的公式),截至频率可用下面的公式计算:

综上所述,正确设置示波器的CDR参数是测量眼图和抖动的关键,测试人员需要参考串行数据规范或仪器厂商的操作文档,才能保证测量的准确性和有效性。

参考文献

1, Fibre Channel – Method Jitter and Signal Quality Specification – MJSQ, T11.2/Project 1315-DT/Rev 14.1, June 5, 2005.

2, Mike Peng Li, "Jitter, Noise, and Signal Integrity at High-speed".

下图1所示为某串行数据链接的系统图,在Fibre Channel、Gigabit Ethernet、SDH等串行链路中都采用了这样的架构。发送端(TX)发送的信号通过信道传输到接收端(RX)后,收发器芯片RX部分的时钟恢复电路从串行数据中恢复出时钟,用恢复的时钟来同步串行数据,进行采样。由于多种原因,进入RX的串行数据信号可能有较大的抖动,理想情况下(锁相环PLL的环路带宽无穷大时),时钟恢复电路的PLL输出的时钟和RX的输入数据信号同相,即零抖动,这时,RX的判别电路(如图1中的D触发器)有最大的建立时间和保持时间余量。但是,由于PLL的环路响应为低通滤波器特性,只能消除串行数据中低频段的抖动,不能处理高频抖动,所以,现实情况中收发器芯片RX端“看到”的眼图是有抖动的。

在图1中,RX端PLL的参数是影响眼图和抖动性能的决定因素。PLL是一种广泛使用的电子电路,可以用于获得特定频率的时钟、射频信号调制与解调和串行数据的时钟恢复。

如图2为PLL的系统图,包括鉴相器(phase detector)、环路滤波器(loop filter)、压控振荡器(voltage controlled oscillator,简称VCO)三个基本部分。PLL的工作原理请参考模拟电路书籍。

在接收端的PLL中,鉴相器、环路滤波器和VCO三部分组成的环路的频响为低通滤波器特性。如下图3所示,接收端的时钟恢复电路的频响是一个低通滤波器,其传递函数为HL,当串行数据信号的抖动变化频率较低时,即从直流到PLL的截至频率,PLL能及时追踪到数据跳变沿(即锁住相位),输出的时钟与输入数据同相(严格讲相位差为固定常数),这样抖动为零。当连续边沿的抖动变化太快时(即存在高频抖动时),PLL不能及时追踪到边沿的变化,于是输出的时钟和数据边沿存在抖动,所以,接收端的CDR不能滤除高于截至频率的抖动,它的抖动传递函数(Jitter Transfer Function简称JTF)的频响为高通滤波特性,接收端CDR又称为TIE抖动的高通滤波器。如图3,抖动传递函数HH=1-HL。

图3:抖动的传递函数

在收发器接收端除了采用如图1所示的PLL来恢复时钟外,另一种时钟恢复方法是使用相位内插器(phase interpolator,简称PI),在FBDIMM和PCI Express中都使用PI来恢复时钟,但是使用仪器测试时,可以用PLL来建模。

测试高速串行数据信号的眼图与抖动的仪器都使用了基于锁相环的时钟恢复方法。其中,实时示波器主要使用软件PLL来恢复参考时钟,取样示波器和误码率测试仪都使用硬件PLL来恢复时钟。实时示波器作为最普及和广泛应用的测试仪器,本文仅介绍实时示波器的软件CDR和眼图测试、抖动测试的关系。

如下图4所示为力科串行数据分析仪中PLL设置的参考,缺省情况下使用FC Golden PLL,该PLL为1阶锁相环,其环路带宽等于比特率除以1667,最早是在Fibre Channel的MJSQ文档中定义的。

图4:力科串行数据分析仪的软件CDR设置界面

如下图5为使用力科示波器测量某2.5Gbps信号,当示波器的串行数据分析软件的PLL带宽在2MHz、5MHz、10MHz、20MHz四种设置下的眼图测量结果,可见,PLL带宽越高,眼图越清晰,抖动越小。问题是,待测试电路的收发器RX端接收到的、真实的眼图和抖动是什么样呢?答案是必须把示波器的CDR参数设置得和待测试电路RX端的CDR参数完全一致,这样示波器的测量结果才具备参考价值。

图5:示波器在不同PLL设置时测量同一信号的眼图

在图4和图5中都是一阶锁相环的CDR,在很多的串行电路标准中都使用这类PLL,比如GBE、XAUI、SDH、CPRI、FC、SAS等等。不过,PCIe Gen2、SATA2、Displayport则使用了二阶锁相环的CDR,如图6所示为一阶PLL和二阶PLL的JTF对比,二阶PLL有更加陡峭的滚降系数-40dB/decade(一阶PLL的滚降系数为20dB/decade)。假设某500kHz的抖动为150ps(而且500kHz在斜线的频段内),通过一阶PLL后抖动只有15ps,而通过二阶PLL后仅为1.5ps。可见,对于图6中低频段的抖动,二阶PLL可以更大幅度的降低该频段的抖动。

图7所示为某2.5Gbps信号,CDR使用一阶PLL或二阶PLL的眼图测量结果,可见,使用二阶PLL得到的眼图非常清晰、抖动更小。二阶PLL可以更大程度的减小低频抖动,通常用于带有扩频时钟(SSC)的串行数据信号,比如计算机主板上的SATA和PCIe。

图7:示波器在不同PLL设置时测量同一信号的眼图

如下图8所示,在力科SDA中,集成了FC Golden, PCIe Gen1, PCIe Gen2, DVI, FBDIMM, USB3.0和Custom多种PLL参数设置,测量时根据待测试信号的类型选择合适的CDR设置。

图8:力科示波器集成了多种PLL设置

在Custom自定义锁相环模式下,可以选择1阶PLL还是2阶PLL。如果是自定义的1阶PLL需要设置极点和零点的频率,PLL的截至频率就是极点频率,零点频率必须高于前者,其决定了阻带的衰减系数;如果是自定义2阶PLL需要设置Natural Frequency(ωn)和Dampling factor(ζ),如图8红色标记所示,该PLL的环路响应的传递函数为H(s)(图8中黄色字体的公式),截至频率可用下面的公式计算:

综上所述,正确设置示波器的CDR参数是测量眼图和抖动的关键,测试人员需要参考串行数据规范或仪器厂商的操作文档,才能保证测量的准确性和有效性。

参考文献

1, Fibre Channel – Method Jitter and Signal Quality Specification – MJSQ, T11.2/Project 1315-DT/Rev 14.1, June 5, 2005.

2, Mike Peng Li, "Jitter, Noise, and Signal Integrity at High-speed".

信号完整性串行数据CD 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)