虚拟示波器/频谱分析仪F-24U结构及原理简介

F-24U除常用的信号测量和频谱分析功能以外,还可以借用现成的工具处理数据的高级应用,如捕捉测量中感兴趣的数据、启动EXCEL电子表格软件、导入包含通道数据的文本文件、生成图表等功能。 下面我们来探究一下F-24U的内部结构和原理。

硬件设计

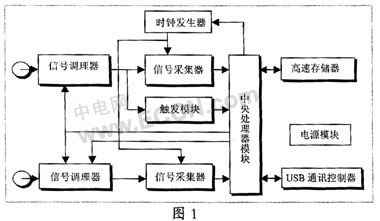

FlashDSO XP USB硬件原理框图如图1所示,主要包括信号调理器、信号采集器、数据传输模块、时钟发生器、中央处理器模块、USB通讯控制器等模块,本文重点介绍信号调理器、信号采集器和数据传输模块。

|

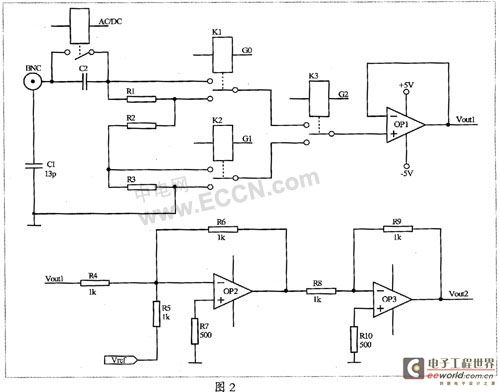

信号调理器信号调理器模块将外部信号转换成信号采集器的输入信号,原理图如图2所示,包含耦合方式、程控衰减、阻抗变换、信号单极性变换等功能,程控衰减部分采用微

型继电器控制,具有耐高压、无电阻及噪音干扰等优点。

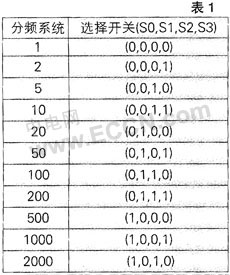

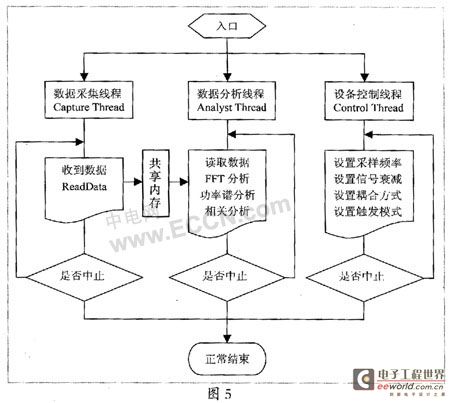

图2中OP1高频放大器作为射极跟随器,提高输入阻抗,对ADC模数转换器提供信号缓冲作用,OP2、OP3组成加法器和反向器,输入Vout1变换为Vout2输出,Vout2=Vout1+Vref,当Vref=2.5V,-2.5V 信号采集器 信号采集器将信号调理器输出的模拟信号通过ADC高速模数转换器,转换成数字信号,同时将信号存入高速静态存储器中,原理图如图3所示,U1模数转换器将输入的信号转换成数字信号,通过U2可编程逻辑器件(CPLD)将数字信号数据写入U3静态存储器中,OP1过零比较器输出信号作为U2的TRIGER触发信号,U2的S0、S1、S2、S3四引脚作为系统时钟分频选择开关,提供11种分频系数,如表1所示,同时U2的T0、T1引脚作为信号触发模式选择开关,提供三种触发模式,如表2所示。 FlashDSO测控软件采用多线程软件技术,软件流程图如图5所示,同时结合表3的命令集完成软件控制命令,系统启动时产生数据采集线程、数据分析线程、设备控制线程三个线程,线程间采用共享内存传输数据。 F-24U(XP)频谱分析仪采用FFT算法实现,频率分辨率df=fs/N,其中,采样频率fs按采样定理确定,不能小于信号中最高频率成份的两倍;N为FFT变换长度,从计算效率、内存空间和屏幕显示点数综合考虑,通常取1024;频率分辨率df越小,频谱分析精度越高,增加采样长度N或减小采样频率都可以达到此目的。

数据传输模块 数据传输模块主要是通过USB接口接收PC机测控软件命令控制相关模块,同时将采集的数据发回到PC机测控软件,原理图如图4所示,具体命令集如表3所示。

软件设计

数据采集线程主要向FlashDSO硬件设备发送命令,将数据传输到PC机共享内存中,同时通知数据分析线程进行相应的处理;数据分析线程读取共享内在中的数据,同时根据数字存储示波器软件界面的菜单选项,通过幅频响应特性、相频响应特性、自相关分析特性、功率谱分析特性进行相应的处理;设备控制线程根据软件界面的选择菜单,设置采样频率、信号衰减、耦合方式、触发模式等。

虚拟示波器频谱分析仪F-24 相关文章:

- 虚拟示波器 频谱分析仪F-24U结构及原理简介(01-12)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)