什么是并行比较型ADC(模数转换器)

1.转换方式

直接转换ADC。

2.电路结构

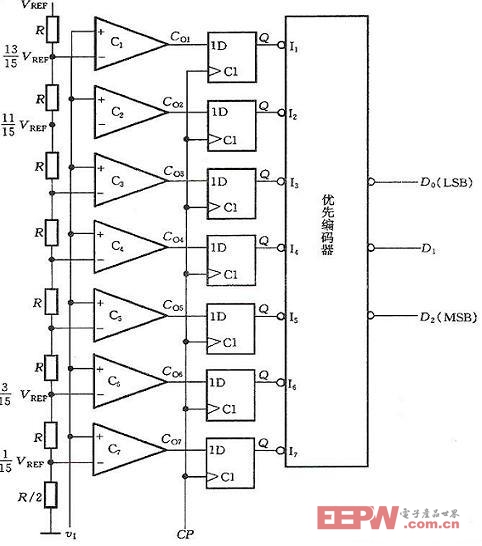

3位并行比较型A/D转换器原理电路如图11.9.1所示。它由电阻分压器、电压比较器、寄存器及编码器组成。

图11.9.1 3位并行A/D转换器

3.工作原理

图中的8个电阻将参考电压VREF分成8个等级,其中7个等级的电压分别作为7个比较器 C1~C7 的参考电压,其数值分别为VREF/15、3VREF/15…、13VREF/15。输入电压为v1,它的大小决定各比较器的输出状态,如当0≤v1 VREF/15时,C7~C1的输出状态都为0;当3VREF/15≤v15VREF/15时,比较器C6和C7的输出CO6=CO7=1,余各比较器的状态均为0。根据各比较器的参考电压值, 可以确定输入模拟电压值与各比较器输出状态的关系。 比较器的输出状态由D触发器存储,经优先编码器编码,得到数字量输出。 优先编码器优先级别最高是I7 ,最低的是I1。

设v1变化范围是 0~VREF,输出3位数字量为D2D1D0,3位并行比较型A/D转换器的输入、输出关系如表10.2.1所示。

表11.9.1 3位并行A/D转换器输入与输出关系对照表

模拟输入 | 比较器输出状态 | 数字输出 | ||||||||

CO1 | CO2 | CO3 | CO4 | CO5 | CO6 | CO7 | D2 | D1 | D0 | |

0≤v1 VREF/15 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

VREF/15≤v13VREF/15 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

3VREF≤v15VREF/15 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

5VREF≤v17VREF | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

7VREF/15≤v19VREF/15 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

9VREF/15≤v111VREF/15 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

11VREF/15≤v113VREF/15 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

13VREF≤v1 VREF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

4.特点

(1)由于转换是并行的,其转换时间只受比较器、触发器和编码电路延迟时间的限制,因此转换速度最快。

(2)随着分辨率的提高,元件数目要按几何级数增加。一个n位转换器,所用比较器的个数为2n-1,如8位的并行A/D转换器就需要28-1=255个比较器。由于位数愈多,电路愈复杂,因此制成分辨率较高的集成并行A/D转换器是比较困难的。

(3)精度取决于分压网络和比较电路。

(4)动态范围取决于VREF。

单片集成并行比较型A/D转换器的产品很多,如AD公司的AD9012(TTL工艺,8位)、AD9002(ECL工艺,8位)、AD9020(TTL工艺,10位)等。

5.改进方法

为了解决提高分辨率和增加元件数的矛盾,可以采取分级并行转换的方法。10位分级并行A/D转换原理如图11.9.2所示。图中输入模拟信号v1,经取样-保持电路后分两路,一路先经第一级5位并行A/D转换进行粗转换得到输出数字量的高5位,另一路送至减发器,与高5位D/A转换得到的模拟电压相减。由于相减所得到的差值电压小于1VLSB,为保证第二级A/D转换器的转换精度,将差值放大25=32倍,送第二级5位并行比较A/D转换器,得到低5位输出。这种方法虽然在速度上作了牺牲,却使元件数大为减少,在需要兼顾分辨率和速度的情况下常被采用。

图11.9.2 分级并行转换10位A/D转换器

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)