低电压带隙基准电压源技术解决方案

本文采用一种低电压带隙基准结构。在TSMC0.13μm CMOS工艺条件下完成,包括核心电路、运算放大器、偏置及启动电路的设计,并用Cadence Spectre对电路进行了仿真验证。

基准电压是数模混合电路设计中一个不可缺少的参数,而带隙基准电压源又是产生这个电压的最广泛的解决方案。在大量手持设备应用的今天,低功耗的设计已成为现今电路设计的一大趋势。随着CMOS工艺尺寸的下降,数字电路的功耗和面积会显著下降,但电源电压的下降对模拟电路的设计提出新的挑战。传统的带隙基准电压源结构不再适应电源电压的要求,所以,新的低电压设计方案应运而生。

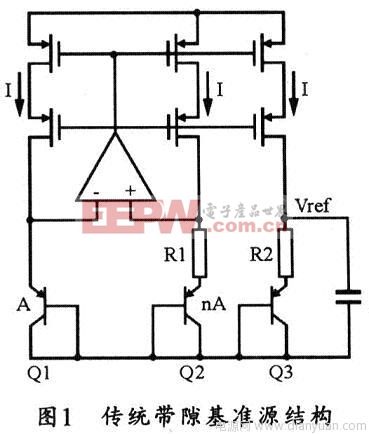

1 传统带隙基准电压源的工作原理

传统带隙基准电压源的工作原理是利用两个温度系数相抵消来产生一个零温度系数的直流电压。图1所示是传统的带隙基准电压源的核心部分的结构。其中双极型晶体管Q2的面积是Q1的n倍。

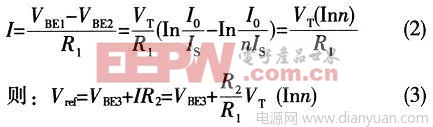

假设运算放大器的增益足够高,在忽略电路失调的情况下,其输入端的电平近似相等,则有:

VBE1=VBE2+IR1 (1)

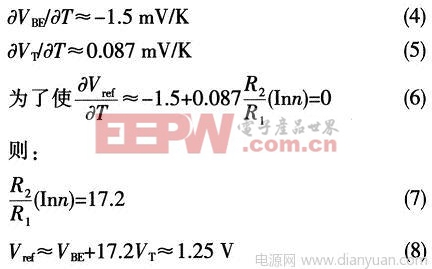

其中,VBE具有负温度系数,VT具有正温度系数,这样,通过调节n和R2/R1,就可以使Vref得到一个零温度系数的值。一般在室温下,有:

但在0.13μm的CMOS工艺下,低电压MOS管的供电电压在1.2 V左右,因此,传统的带隙基准电压源结构已不再适用。

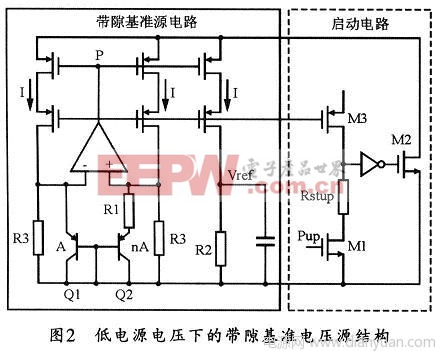

2 低电源带隙基准电压源的工作原理

低电源电压下的带隙基准电压源的核心思想与传统结构的带隙基准相同,也是借助工艺参数随温度变化的特性来产生正负两种温度系数的电压,从而达到零温度系数的目的。图2所示是低电压下带隙基准电压源的核心部分电路,包括基准电压产生部分和启动电路部分。

2.1 带隙基准源电路

由于放大器的输入端电平近似相等,故由电流镜像原理可得到如下等式:

这样,适当选择R2/R1、R2/R3以及n的值,即可得到低电源电压下的基准电平。

基于版图的设计考虑,可选择n为8,这样可以更好地实现三极管的匹配,减小误差。该电流源使用共源共删结构,从而可以提高电流拷贝的精度以及减小电源电压对Vref的影响,并在一定程度上有利于PSRR。

虽然CMOS工艺中的电阻绝对值会有偏差,但这里用到的是电阻的比值,所以要尽可能的做到比值的准确。具体方法是把R1、R2、R3都用单位电阻并联串联来表示。版图设计时,应尽量把这些电阻放在一起,并在周围加上dummy,以最大限度地减小工艺偏差对电阻比值的影响。

2.2 启动电路

电路开启前,可将Pup置为0,开关M1关断,反相器输入端为高电平,开关M2不开;当信号Pup置为1时,开关M1打开,反相器输入端电压被拉低,使开关M2开启,P点电压被拉低,带隙基准电路部分开始工作,M3随之开启;此后由于M3开始工作,电阻Rstup上流过的电流把反相器输入端电位抬高,超过反相器反向电压时。输出为低电位,开关M2关闭,启动电路结束工作。M3与Rstup的选取是启动电路值得注意的地方,M3镜像而来的电流与Rstup的阻值乘积得到的电压值必须在P点电压稳定前足以使反相器输出低电压,并使开关M2关断。

3 仿真分析

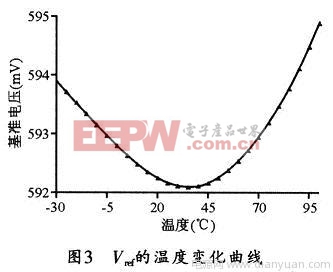

图3为基准电压幅度随温度变化的曲线,可以看到,从-30~100℃,Vref基本在3 mV以内波动,误差范围在5%以内。

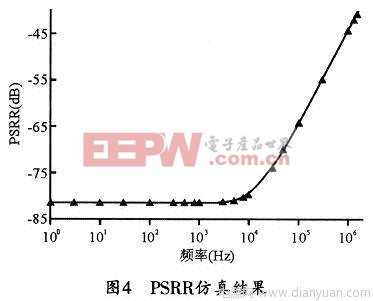

图4所示是本设计的PSRR仿真结果。从图4可以看出,在低频时,其PSRR约为-81 dB。

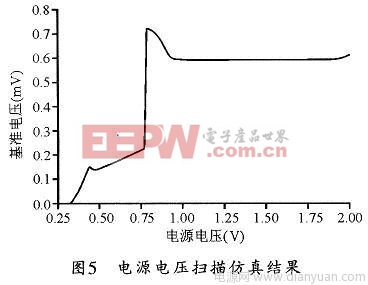

图5是本设计的电源电压扫描仿真结果。由图可见,其电源电压在1~1.8 V之间,基准电路都能很稳定的输出约600 mV的电压基准值。

4 结束语

本文给出了一个低电压供电时的带隙基准电压源电路的设计方法。该电路通过对传统带隙基准电路的改进,使输出基准电压在600 mV仍然能满足零温度系数。本设计基于TSMC 0.13 μmC-MOS工艺。通过仿真,结果显示:该电路在-30~100℃范围内的温度系数为12×10-6℃,低频下的PSRR约为-81 dB。在供电为1~1.8 V范围内,电路能够工作正常,输出电压约600 mV。

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)