解决电源噪声的新思路

时间:02-23

来源:互联网

点击:

自上市以来,CMOS 单电源放大器就让全球的单电源系统设计人员受益非浅。影响双电源放大器总谐波失真加噪声 (THD+N) 特性的主要因素是输入噪声和输出级交叉失真。单电源放大器的 THD+N 性能源于放大器的输入和输出级。然而,输入级对 THD+N 的影响又让单电源放大器的这种规范本身复杂化。

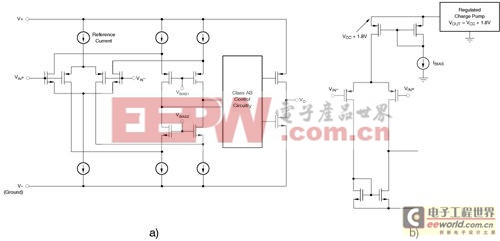

有两种单电源放大器拓扑可以接受电源之间的输入信号。图 1a 所示拓扑具有一个互补差动输入级。在该拓扑中,放大器的输入位于负轨附近时,PMOS 晶体管为“开”,而 NMOS 晶体管为“关”。当放大器的输入更接近于正电压轨时,NMOS 晶体管为“开”,而 PMOS 晶体管为“关”。

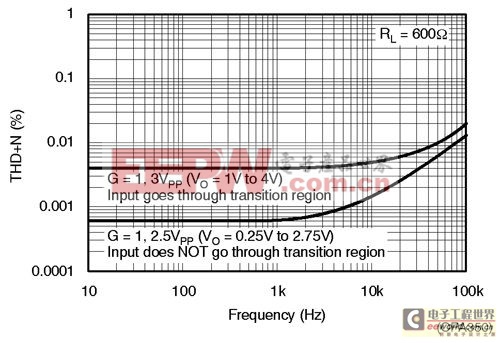

这种设计拓扑在共模输入范围会存在极大的放大器失调电压差异。在接地电压附近的输入范围,PMOS 晶体管的失调误差为主要误差。在正电源附近的区域,NMOS 晶体管对主导失调误差。由于放大器的输入通过这两个区域之间,因此两个对均为“开”。最终结果是,输入失调电压将在两个级之间变化。当 PMOS 和 NMOS 均为“开”时,共模电压区域约为 400 mV。这种交叉失真现象会影响放大器的总谐波失真 (THD)。如果您以一种非反相结构来配置互补输入放大器,则输入交叉失真就会影响放大器的 THD+N 性能。例如,在图 2 中,如果不出现输入过渡区域,则 THD+N 等于0.0006%。如果 THD+N 测试包括了放大器的输入交叉失真,则 THD+N 等于 0.004%。您可以利用一种反相结构来避免出现这类放大器交叉失真。

另一个主要的 THD+N 影响因素是运算放大器的输出级。通常,单电源放大器的输出级有一个 AB 拓扑(请参见图 1a)。输出信号做轨至轨扫描时,输出级显示出了一种与输入级交叉失真类似的交叉失真,因为输出级在晶体管之间切换。一般而言,更高电平的输出级静态电流可以降低放大器的 THD。

放大器的输入噪声是影响 THD+N 规范的另一个因素。高级别的输入噪声和/或高闭环增益都会增加放大器的总 THD+N 水平。

要想优化互补输入单电源放大器的 THD+N 性能,可将放大器置于一个反相增益结构中,并保持低闭环增益。如果系统要求放大器配置为非反相缓冲器,则选择一个具有单差动输入级和充电泵的放大器更为合适。

有两种单电源放大器拓扑可以接受电源之间的输入信号。图 1a 所示拓扑具有一个互补差动输入级。在该拓扑中,放大器的输入位于负轨附近时,PMOS 晶体管为“开”,而 NMOS 晶体管为“关”。当放大器的输入更接近于正电压轨时,NMOS 晶体管为“开”,而 PMOS 晶体管为“关”。

图 1 互补输入级、单电源放大器:a)。带一个正充电泵的单差动对输入级:b)

这种设计拓扑在共模输入范围会存在极大的放大器失调电压差异。在接地电压附近的输入范围,PMOS 晶体管的失调误差为主要误差。在正电源附近的区域,NMOS 晶体管对主导失调误差。由于放大器的输入通过这两个区域之间,因此两个对均为“开”。最终结果是,输入失调电压将在两个级之间变化。当 PMOS 和 NMOS 均为“开”时,共模电压区域约为 400 mV。这种交叉失真现象会影响放大器的总谐波失真 (THD)。如果您以一种非反相结构来配置互补输入放大器,则输入交叉失真就会影响放大器的 THD+N 性能。例如,在图 2 中,如果不出现输入过渡区域,则 THD+N 等于0.0006%。如果 THD+N 测试包括了放大器的输入交叉失真,则 THD+N 等于 0.004%。您可以利用一种反相结构来避免出现这类放大器交叉失真。

图 2 一个互补输入级单电源放大器的 THD+N 性能

另一个主要的 THD+N 影响因素是运算放大器的输出级。通常,单电源放大器的输出级有一个 AB 拓扑(请参见图 1a)。输出信号做轨至轨扫描时,输出级显示出了一种与输入级交叉失真类似的交叉失真,因为输出级在晶体管之间切换。一般而言,更高电平的输出级静态电流可以降低放大器的 THD。

放大器的输入噪声是影响 THD+N 规范的另一个因素。高级别的输入噪声和/或高闭环增益都会增加放大器的总 THD+N 水平。

要想优化互补输入单电源放大器的 THD+N 性能,可将放大器置于一个反相增益结构中,并保持低闭环增益。如果系统要求放大器配置为非反相缓冲器,则选择一个具有单差动输入级和充电泵的放大器更为合适。

- 带反并联二极管IGBT中的二极管设计(07-11)

- EMI/EMC设计讲座(三)传导式EMI的测量技术(07-20)

- 通信开关电源的EMI/EMC设计(07-22)

- 一种用于航天工程的二次电源系统设计(07-22)

- 单片式开关电源在电器控制系统中的应用(07-25)

- 有源功率因数校正技术在开关电源中的应用研究(07-25)