TI技术分析:数字接口系列文章之SPI 总线

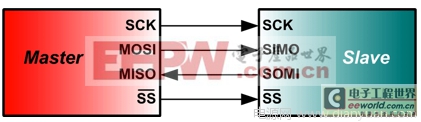

串行外设接口 (SPI) 总线是一种运行于全双工模式下的同步串行数据链路。用于在单个主节点和一个或多个从节点之间交换数据。SPI总线实施简单,仅使用四条数据信号线和控制信号线(请参见图 1)。

尽管表1中的引脚名称取自Motorola公司的SPI标准,但特殊集成电路的SPI端口名称通常与图1中所标示的名称有所不同。

图1 基本的SPI总线

表1 SPI引脚名称分配

SPI数据速率通常介于1到70MHz 之间,字节长度范围从8位和12位到这些数值的倍数位。

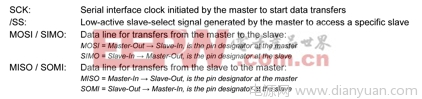

数据传输通常会包含一次数据交换。当主节点向从节点发送数据时,从节点也会向主节点发送数据。为此,主节点的内部移位寄存器和从节点被设置成环形(请参见图 2)。

图2 两个移位寄存器形成一个内部芯片环形缓冲器

在数据交换之前,主节点和从节点使其内部移位寄存器加载存储器数据。产生时钟信号时,主节点会通过MOSI线同步输出其移位寄存器。同时,从节点在SIMO处从主节点读取第一位,并将其存储到存储器中,然后通过SOMI输出MSB。主节点会在MISO处读取从节点的第一位,并将其存储到存储器中以待稍后处理。整个过程将一直持续,直至交换完所有数据位,然后主节点使时钟空闲并通过 /SS禁用从节点。

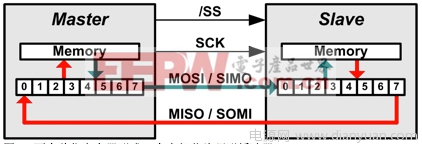

除设置时钟频率之外,主节点还会配置相对于数据的时钟极性和时钟相位。这两个选项分别称作CPOL和CPHA,能够允许时钟信号实现180度相移且数据延迟半个时钟周期。图3显示了相应的时序图。

图3 时钟极性和相位的时序图

CPOL=0时,时钟在逻辑0处空闲:

* 如果CPHA=0,数据会在SCK的上升沿上读取,在下降沿上变化。

* 如果CPHA=1,数据会在SCK的下降沿上读取,在上升沿上变化。

CPOL=1时,时钟在逻辑高电平处空闲:

*如果CPHA=0,数据会在SCK的下降沿上读取,在上升沿上变化。

*如果CPHA=1,数据会在SCK的上升沿上读取,在下降沿上变化。

在SPI中,主节点可以与单个或多个从节点进行通信。在使用单个从节点的情况下,从选择信号可以关联到从设备的本地接地电位以允许永久接入。对于使用多个从节点的应用,可能有两种结构:独立和菊花链式从节点(请参见图 4)。

图4 主节点与独立从节点(左)以及菊花链式从节点(右)进行通信

从节点独立寻址时,主节点必须提供多个从选择信号。该结构一般用在数据采集系统中,其中的多个模数转换器 (ADC) 和数模转换器 (DAC) 都必须单独接入。

菊花链式从节点需要主节点提供唯一的从选择信号,因此该结构要求同时启用所有从节点,以确保菊花链内通过所有移位寄存器的数据流不会中断。典型的应用为工业级I/O模块中的级联多通道输入串行器和输出驱动器。

作者简介:

Thomas Kugelstadt现任TI高级系统工程师,主要负责定义新型高性能模拟产品以及探测和调节工业系统中低电平模拟信号的完整系统解决方案的开发工作。

在TI工作的20年间,他曾被派往欧洲、亚洲以及美国担任过各种国际应用职位。 Thomas毕业于法兰克福应用技术大学 (Frankfurt University of Applied Science),一毕业就成为一名见习工程师 (Graduate Engineer)。

SPI总线 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)