基于SOC技术的LED灯序电路设计

本文介绍了一种基于最新SOC技术的简单的8 LED灯序电路设计。在这个设计中最精彩的部分就是微处理器无需进行干预。不是采用传统的由单片机处理器干预的被动的数字外设,此设计完全是基于SOC数字系统的智能分布式处理功能。这使中央处理器从管理灯序电路的工作中解脱出来,节省CPU资源从而设计效率更高。

该设计方法可以很容易的扩展到LED以外的需要用指定顺序开启或关闭的其他设备,比如不同长度、不同模式的序列定时器等等。该设计示例中还有额外的功能:

· 7位计数器(TC)终端计数

· 指示设备开启关闭的输出

· 为序列器件提供的8位输出

· 给Verilog状态机的时钟输入

· 给8位ALU(bit-slice)处理器的总线时钟

这篇文章中用到的开发工具是赛普拉斯半导体可编程片上系统(PSoC)的集成开发环境PSoC Creator。

原理图设计

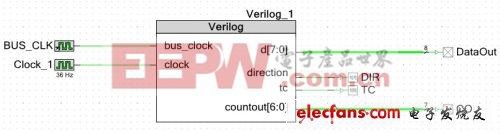

设计的第一步是在创建一个Verilog符号来定义输入、输出和与之相关的位宽度(见图1)。一旦上层Verilog模型(原理图)已经建立,它就可以用来产生包含所有模块中引脚定义的Verilog源文件。这一步不需要开发功能Verilog代码。

图1:Verilog 符号。

刚才创建的Verilog符号现在可以放置到高层原理图设计。在这里,每一个输入及输出都能连接到时钟源、I / O引脚、状态和控制寄存器等等。8-LED灯序电路高层原理设计见图2。

图2:高层原理设计示例。

到现在为止,Verilog符号已经建立,放置到了高层原理设计里,并且连接到了设备的I/ O和时钟。现在可以生成Verilog代码来履行某些功能,在这个案例中可使发光二极管闪烁。为了管理序列的逻辑能力,可以在设计里引入一个简单的数据路径。

这个数据路径包含一个8位ALU,其具备精简指令集,两个数据寄存器、两个累积器、位移和比较逻辑、一个4 deep的 8位FIFO。为了保持设计简单,只用到了两个ALU,用来将累加器设置为0,每次开启或关闭序列执行的时候累加器就递增。对于较复杂的定序设计,开发人员可以联合多个ALU形成一个16位或24位处理器。这样的处理器类似于bit-slice处理器,其在70年代和80年代早期比较流行,它可以为次序的子系统提供足够的处理能力,。

数据路径配置工具示图如下。请注意CFGRAM(配置RAM)的前二行注释:“A0 - 0”,这是给累加器0清零,“A0 - A0+1”,实现在A0累加值。

图3:数据路径配置工具。

片上系统(SOC)技术以可编程的方式重新利用了bit-slice技术,用来把处理任务智能地分配到其他可编程硬件,从而减少主CPU的负荷。使用这种方法,可以研制出一种标准状态机。不同的是,通常算法功能要消耗大量的逻辑门。而在新的方式中这已无需再关注,因为这些功能在标准标准ALU即可实现,它包含由基于PLD的状态机控制的数据路径与/或逻辑。

这个设计独立运行于主CPU。主应用程序可以通过API(可以修改执行参数)控制灯序电路,灯序电路初始化之后,就不再需要CPU。此外,这种实现方式同使用CPU方式相比,本身即可提高效率、可以使用更少的晶体管,从而更好的降低整体系统功耗,给其他特性预留出更多资源。

本文讨论了LED灯序电路设计,同样的设计方法也可用到类似设计,可以通过功能强大的SOC集成结构来执行各种各样的需要频繁处理的任务,降低主CPU负荷。现在,工程师不断面临很多压力:提高性能、降低功耗、减少成本…拥有一种像这样的系统设计工具可以帮助工程师不断地创造奇迹,达到公众对他们的期望。

- 分享:基于功放保护电路的设计分析与检测(12-09)

- 电源电路设计中常用测试仿真软件(12-09)

- 电路设计中主动PFC的优缺点分析(12-07)

- 开关电源电路设计的元器件选择(12-07)

- 10T真空电弧炉用40kA直流电源的研制与应用(12-07)

- GP02开关电源电路设计介绍(12-05)