0.18 μm CMOS带隙基准电压源的设计

本文提出了一种基于0.18 μm标准CMOS工艺的高性能带隙基准电压源的设计方法,输出基准电压0.6 V,输入电压范围为1.5 V~3 V,温度系数仅为5 ppm/℃,功耗为80 ?滋W.

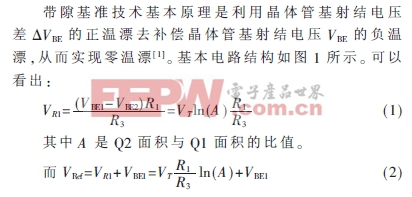

1 带隙基准技术基本原理

基准电压源已成为大规模、超大规模集成电路和几乎所有数字模拟系统中不可缺少的基本电路模块。基准电压源可广泛应用于高精度比较器、A/D和D/A转换器、随机动态存储器、闪存以及系统集成芯片中。带隙基准电压源受电源电压变化的影响很小,它具备了高稳定度、低温漂、低噪声的主要优点。

其中,VT具有正温度系数,VBE1具有负温度系数,则输出VRef的温度系数可以调整到接近零。

2 带隙基准源设计电路

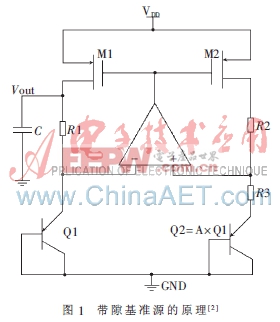

为了得到较低的输出电压,在两个晶体管支路上分别并联一个电阻,根据此原理,设计电路图[3]如图2所示。

三个PMOS管为同样宽长的MOS管,均处于饱和工作状态,根据镜像原理有:

由式(7)可以看出,调节R2/R1与R2/R0的值,就可以得到零温度系数的电压输出值。虽然电阻本身也具有温度系数,但在此电路中,输出电压只与电阻之间的比值有关,所以电阻的温度系数对输出的影响很小。

3 运算放大器的设计

以上推理仅适用于运算放大器工作在理想状态的情况,图2电路的最主要部分就是运算放大器,运算效果的优劣决定着此基准电压源的效果。根据电路的需求,设计的运放有较高的放大倍数、较低的功耗、较低的噪声,所以选用普通的两级运放即可,电路图如图3所示。

图3中PM0和PM1作为镜像电流源,将偏置电流4 μA镜像给放大器使用,PM3与PM4作为运放的输入端,比使用NMOS差分对得到更大的输入范围,两级的级联运放需要加入相位补偿电路(图3电路中串联的电阻R和电容C支路[4]),仿真后的幅频响应如图4所示。

从图4可以看到运算放大器的幅频响应,相位裕度为46°,低频段增益达105 db。

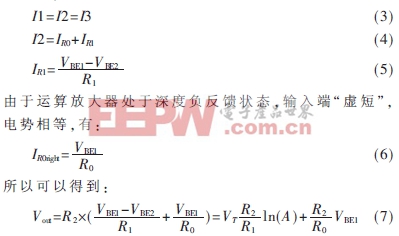

4 整体电路

为了使电路能够正常的工作,加入启动电路,整体电路如图5所示。

5 仿真结果

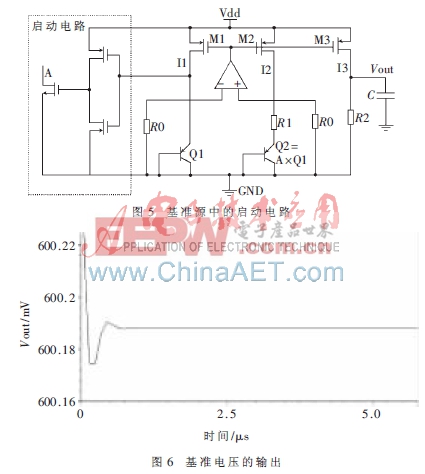

依照图5,在Cadence中使用SMIC 0.18 μm工艺库搭建电路,进行仿真。电路的启动时间及输出电压如图6所示。

可以看到,输出的基准电压稳定后在600.19 mV,启动时,有微小的变化,并且在极短的时间内稳定下来。

仿真基准电压源的温度系数和在电源电压变化时的稳定性如图7所示。

在图7中,可以看到温度从0 ℃~100 ℃变化时,基准电压从600.19 mV增大至600.44 mV,后逐渐变小至600.14 mV,温度系数为5 ppm/℃。

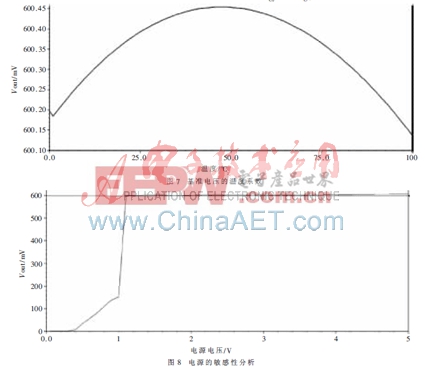

仿真图5中电源电压变化对输出基准电压的影响,得到结果如图8所示。

从图8中可以看到,电源电压从0 V增大到5 V,在电源电压为1.1 V时,输出的基准电压已经达到600 mV,而在当电源电压继续增大时,输出的基准电压基本保持不变。

本文使用SMIC0.18μm工艺设计实现了一个0.6 V的带隙基准电压源,并且功耗较小,适用于各种便携式电路设计中基准源的需要,仿真结果证明了该电路良好的性能。

参考文献

[1] ROBERT P.The design of Band-Gap reference circuits:Trials and Tribulations[C].IEEE 1990 Bipolar Circuits and Technology Meeting,1990:214-218.

[2] ROBERT P.The design of Band-Gap reference circuits:Trials and Tribulations[C].IEEE 1990 Bipolar Circuits and Technology Meeting,1990:214-218.

[3] RAZAVI B.Design of CMOS integrated circuits:317-32.西安交通大学大学出版社.2002,12.

[4] JACOB R,HARRY B,ADVID W I,et al.CMOS circuit design,Layout,and Simulation:485-489.机械工业出版社.2006,1

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)