DSP系统中噪声和EMI问题的解决方案

之一就是为信号电流提供最小的电感回路。这可以利用电源平面和地平面来实现。电源平面通过形成自然的高频退耦电容将寄生电感降到最校而地平面形成一个屏蔽面,即众所周知的镜像平面,能够提供最短的电流回路。

一种有效的PCB布线方法就是将电源平面和地平面靠在一起。这样形成了高平板电容和低阻抗,有利于降低噪声和辐射。为了屏蔽,最好的选择是:关键信号最好布到靠近地平面一边,而其余的则应靠近电源平面一侧。

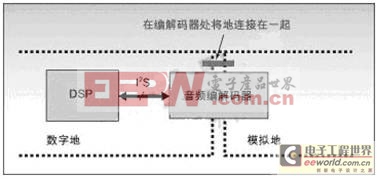

在高速视频系统中,保持回路短的目的意味着视频地不能被隔离。而必须被隔离的音频地,绝不能在数据输入点处短接到数字地上,如图2所示。

图2:音频地隔离。

电源隔离和锁相环

如何实现最佳供电是控制噪声和辐射的最大挑战。动态负载开关环境很复杂,包括的因素有:进入和退出低功率模式;由总线竞用和电容器充电所引起的很大的瞬态电流;由于退耦和布线不合理引起较大的电压下降;振荡器使线性调节器输出过载。

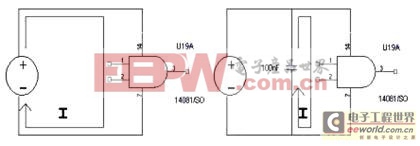

图3给出了一个设计电流回路的实例,其中利用了电源线退耦。该例中的退耦电容尽可能靠近DSP。如果没有退耦,动态电流回路将较大,这将加大电源电压的降幅,从而产生电磁辐射。

图3:电源退耦。

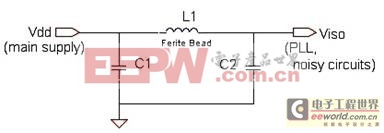

为PLL供电时,电源隔离是非常重要的,因为PLL对噪声非常敏感,并且对于稳定系统来说,要求抖动非常低。你还需要选择模拟的还是数字的PLL,模拟PLL对噪声的敏感度比数字PLL要低。

图4:PLL电源隔离。

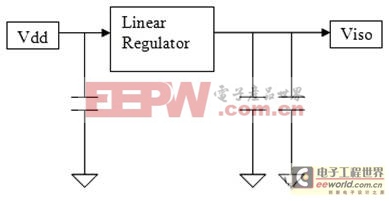

如图4所示的具有低截至频率的∏型滤波器经常被用来将PLL与系统中的其他高速电路隔离开。一个较好的办法是利用一个低压差(LDO)电压调整器来独立产生PLL的电源电压,如图5所示。该方法虽增加了成本,但确保了低噪声和优异的PLL性能。

图5:利用LDO实现PLL电源的隔离。

串扰及传输线效应

信号间的干扰,即串扰,可以通过电磁辐射在印制线间传播。这也可能由电源和地平面上的无用信号以电气的形式产生。串扰与印制线间距的平方成反比。因此,为了将串扰减到最小,单端信号的布线间距应至少是印制线宽度的2倍。对于像以太网和USB这类的差分信号,印制线间距需要与印制线宽度相同,目的是能够与差分阻抗相匹配。关键信号可以用地和电源平面进行屏蔽,或者在改板时增加与信号并行的地线。

有些信号还产生引起串扰的高频谐波。由于辐射的能量正比于信号的上升和下降时间,较慢的上升或下降时间引起的干扰将较小。图6显示出视频干扰的实例,这些干扰可能由内部时钟的辐射所引起。在北美地区第二频道中,18.432MHz的音频时钟的三次谐波,将产生如图中左侧所示的干扰。通过在音频时钟印制线上增加一个串联电阻来放慢时钟的上升和下降时间,减小了干扰,其结果如图6中的右侧所示。不过,设计师需要了解定时裕度,以便于将上升和下降沿降低到系统所允许的限度内。

图6:解决音视频串扰。

与串扰相关的是传输线效应,这种效应在高速印制线变成产生辐射干扰的发射器时产生。通常,当信号的上升时间小于传播延迟的2倍时,印制线才发射信号。这就暗示出了一个经验,即为了减小传播延迟,印制线的长度应尽可能短。另一个是合理的信号端接将减慢信号的上升时间,从而将反射引起的过冲和欠冲减到最小。图7显示了如何利用并行端接来校正电平并将传输线效应减到最小。

图7:利用端接将传输线效应减到最小。

设计师可能会质疑,既然芯片内部已经集成了电阻,在外部端接负载电阻是否还有其重要性。实际上,除了控制传输线效应外,外部电阻还可以实现信号完整性的精密调整。DSP无法与电路板阻抗完全匹配,因此端接负载可以减小源电流,以及上升和下降时间。

与外部端接负载电阻一样,外部的上拉和下拉电阻也是重要的。对于无连接的引脚来说,虽然内部的上拉和下拉电阻是足够的,但高速开关噪声能够传过来,并会误触发连接端上的内部逻辑。

控制EMI

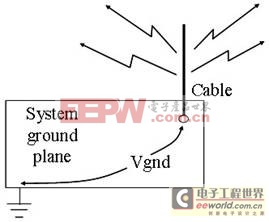

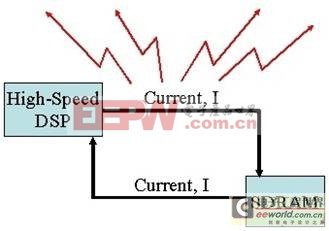

能够辐射到系统外的辐射被认为是EMI,这可能使设计无法通过FCC认证。有两种可能的辐射:一种是发射源是一条直线型的信号印制线,或者电缆的共模辐射,另一种是其信号和回路构成一个大电流环路的差分模式辐射。共模辐射随着频率的升高而降低,而差分模式辐射则随着频率的升高而增强,直到其饱和点。这两种模式的辐射如图8和9所示。

图8:共模辐射。

图9:差模辐射。

如何处理EMI取决于辐射源。对于共模辐射,当EMI来自外部电缆时(例如图8所示的情况),可以在电缆上加一个扼流圈。如果导致EMI的是内部传输线,则通常用端接负载的方式,不过在信号印制线间加入一条地线也有助于减小辐射。另一种可能的方案是将信号的印制线长度减短至小于信号波长(或信号频率的倒数

- DSP系统中延迟电池寿命关键--DC/DC稳压器(12-05)

- 集成工具提高嵌入式DSP系统设计与自动化程度(01-17)

- DC-DC开关稳压器在DSP系统中的应用(05-16)

- 新型DC-DC开关转换器设计:在DSP系统中延长电池寿命(05-05)

- 电缆故障源有效冲击放电信号测量电路设计(12-09)

- 总结反激式电源常见噪声源及解决方案(12-09)