电源设计技巧:DDR内存电源

CMOS逻辑系统的功耗主要与时钟频率、系统内各栅极的输入电容以及电源电压有关。器件形体尺寸减小后,电源电压也随之降低,从而在栅极层大大降低功耗。这种低电压器件拥有更低的功耗和更高的运行速度,允许系统时钟频率升高至千兆赫兹级别。在这些高时钟频率下,阻抗控制、正确的总线终止和最小交叉耦合,带来高保真度的时钟信号。传统上,逻辑系统仅对一个时钟沿的数据计时,而双倍数据速率 (DDR) 内存同时对时钟的前沿和下降沿计时。它使数据通过速度翻了一倍,且系统功耗增加极少。

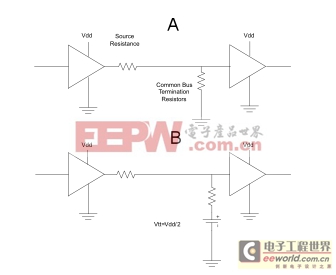

高数据速率要求时钟分配网络设计要倍加小心,以此来最小化振铃和反射效应,否则可能会导致对逻辑器件非有意计时。图1显示了两种备选总线终止方案。第一种方案(A)中,总线终止电阻器放置于分配网络的末端,并连接至接地。如果总线驱动器处于低态下,电阻器的功耗便为零。在高态下时,电阻器功耗等于电源电压(VDD)平方除以总线电阻(源阻抗加端接电阻)。平均功耗为电源电压平方除以两倍总线电阻。

图1 VTT 端接电压降低一半端接功耗

第二种方案(B)中,端接电阻器连接至电源电压 (VTT),电源电压为VDD电压的一半。电阻器功耗恒定,且与电源电压无关,其等于 VTT(或(Vdd/2))平方除以端接电阻。相比第一种方法,这种方法产生的功耗仅为其1/2,但需要增加一个电源。同时,它对电源的要求有些特别。首先,其输出需要为驱动器电压 (VDD)的一半;其次,它需要同时输出电流和汲取电流。当驱动器输出电压为低时,电流来自VTT电源。然而,当驱动器为高电平时,电流流入电源。最后,电源还需要在系统数据变化时在各模式之间转换,且必须提供低源阻抗,直到接近系统的时钟速率。

根据端接电阻、时钟频率和系统电容,确定峰值功耗相对容易。估算平均功耗要更困难一点,它可以比1/10峰值功耗低好几倍。由于系统为动态且没有真正固定不变的时钟率,并非每个周期都对数据计时,而且会有一些三态的器件,因此您需要考虑所有这些因素。

平均电流是验证系统测量的一个重要数值,因为它对确定正确的电源拓扑很重要。例如,您可能会在开关式电源低功耗和线性稳压器的低成本和小体积之间进行权衡。表1显示了开关式电源和线性稳压器在组件数目、面积要求、功耗和成本等方面的对比情况。该表适用于可输出3安峰值电流的一些稳压器。有趣的是,如果峰值电流一直存在的话,就很难处理高功耗。建立DC电流将有助于做出正确的选择。很明显,从各个方面来看,线性稳压器都是更佳的选择。

表1 线性方法体积更小、成本更低但不如开关式电源高效。

DDR电源面临的一个巨大挑战是在高瞬态负载极端情况下如何控制输出电压。如表1所示,线性方法拥有比开关方法更宽的控制带宽。因此,它使用更小的电容器来控制输出阻抗。例如,3安负载下要将输出控制在40mV以内,交叉频率的输出阻抗需要小于0.013 Ohms,相当于约10 uF电容。50kHz下线性控制环路关闭的开关式电源使用200uF的电容,从而带来更多的成本和电路板面积。

总之,DDR内存通过同时对时钟两个沿的数据计时提高了系统速度,带来更高的数据传输速度。由于是高频运行,要求使用端接电阻器来降低电压反射。通过将一端同一半电源电压的电压连接,可以最小化端接的损耗。这种电源需要能够输出或者汲取电流,同时还必须具有高交叉频率,来最小化电容器要求。如果升高的功耗在可接受范围以内,则端接电源的线性稳压器方法可以节省成本和减小体积。

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)

- 电源设计必看:开关电源设计经典问答(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流--第 2 部分(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流-第 1 部分(12-09)

- 电源设计控制的利弊权衡(12-09)