低成本紧凑型荧光灯镇流器设计

由于功率电平较低,集成紧凑型荧光灯(CFL)镇流器通常不需要进行功率因数校正(PFC)。然而,随着这款具有节能优势的产品的市场需求日益旺盛,在不久的将来,功率因数校正将很有可能成为一项强制性标准。有源PFC电路要求采用附加的控制集成电路、电感、二极管和高压MOSFET.无源PFC电路成本较低,但会增加灯电流波峰因数,从而缩短灯的使用寿命。本文所述设计采用了一个简单的控制电路来改良无源PFC电路,可以在实现较高功率因数的同时,将灯电流波峰因数降至可接受的水平。

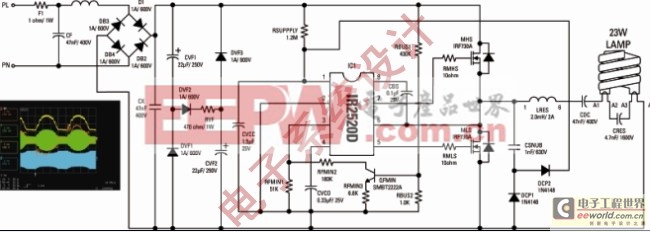

图1所示为建议的紧凑型荧光灯镇流器设计示意图。该镇流器包含一个具备EMI滤波器的交流输入级,一个无源PFC级,一个采用国际整流器公司IR2520D自适应镇流器控制IC的镇流器控制级,一个半桥逆变器和谐振输出级。相比于现有的CFL电路,这个设计的改进之处在于用填谷式无源PFC电路和灯电流波峰因数控制电路来实现较高的功率因数、较低的总谐波失真(THD)和可接受的灯电流波峰因数。

图1:采用IR2520D的电子CFL镇流器电路。上:直流总线(黄色);中前:Iinput(红色);中后:ILAMP(绿色);下:VLamp(蓝色)。

填谷式无源PFC电路由CVF1-2、DVF1-3、RVF和CX组成(图1)。在被整流交流输入的每个半波期间,电容CVF1和CVF2经由二极管DVF2和电阻RVF而被串联充电至交流峰值电压的1/2.RVF的作用是在对电容器进行充电的过程中,降低电流波形的波峰。当总线电压随正弦波波形下降至Vpeak/2之后,电容开始提供输出电流。此时,这两个电容本质上呈并联状态,并一直提供负载电流,直至被整流交流输入在下一个半波期间再次超过Vpeak/2.电容CX的作用是滤除直流总线上出现的半桥逆变器开关尖峰。这个填谷式无源PFC电路实现了良好的功率因数(》0.9)和较低的THD(《30%),但其主要缺点是,50%的直流母线纹波会导致很高的灯电流波峰因数,从而缩短灯的使用寿命。

除IR2520D之外,还有一个由RFMIN2-3、RBUS1-2和QFMIN构成的控制电路,通过调制工作频率来降低灯电流波峰因数。如果镇流器工作频率固定,那么,填谷式电路造成的50%直流总线纹波会产生很高的灯电流波峰因数,因为直流总线电压越高,谐振输出级产生的灯电流也越高。由于IR2520D采用了具备外部可编程最小频率的VCO,因此,半桥逆变器开关频率取决于VCO管脚上的电压和连接至FMIN管脚的电阻的阻值(请参见http://www.irf.com网站提供的IR2520D数据表)。当直流总线达到一定电压时,与分压器(由RBUS1和RBUS2构成)相连的QFMIN的基极电压将超过QFMIN的导通阈值,而使得QFMIN导通。此时,RFMIN1与串联的RFMIN2和RFMIN3的并联组合,构成了FMIN管脚与GND之间的电阻。由于FMIN管脚上的电阻越低,则开关频率越高,因此,在接近直流总线峰值时的逆变器开关频率将高于其谷底时的逆变器开关频率。这样,由ILAMP(pk)/ILAMP(avg)计算得到的波峰因数值将降低。RFMIN3是一个发射极负反馈电阻,可用于改善线性。如果没有RFMIN3,当QFMIN基极上的电压达到阈值时,QFMIN将快速接通。这将导致工作频率骤升,而造成灯电流波形失真。

总而言之,该设计是一种能够实现高功率因数(0.96)、低THD(28.5%)和可接受的灯电流波峰因数(1.71)的低成本CFL镇流器电路。相比之下,典型的CFL镇流器则功率因数较低(0.56)、THD较高(128%),同时具有类似的波峰因数(1.71)。这种镇流器不仅控制方法简单,元器件数量较少,而且此设计还满足了镇流器所必需的全部要求。

- Hf荧光灯电子镇流器的评价(07-22)

- NXPUBA2016A35WTL5高效荧光灯电源解决方案(12-24)

- 荧光灯电子镇流器的电路分析(04-14)

- 荧光灯调光电子镇流器的设计(03-20)

- 半导体荧光灯原理简介(04-13)

- DALI技术及NEC 78K0/IX2调光方案介绍(03-22)