电源管理技术及计算

引言

本应用笔记讨论电源管理技术及计算C8051F00x和C8051F01x SoC中的功率消耗的方法。很多应用系统对功耗有严格的要求,也存在几种不以牺牲性能为代价的降低功耗的方法。计算预计功耗对于说明系统的供电要求是很重要的。

关键点

供电电压和系统时钟频率对功率消耗有很大影响。

C8051F的SoC有两种电源管理方式:等待和停止。

功率消耗可以作为系统时钟、电源电压和被允许的外设的函数来计算。

降低功耗的方法

CMOS数字逻辑器件的功耗受供电电压和系统时钟(SYSCLK)频率的影响。可以通过调整这些参数来降低功耗,设计者也很容易控制这些参数。本节讨论这些参数及它们对功率消耗的影响。

降低系统时钟频率

在CMOS数字逻辑器件中 功耗与系统时钟(SYSCLK)频率成正比:

功耗 = CV2f

其中:C是CMOS的负载电容,V是电源电压,f是SYSCLK的频率。

方程1. CMOS功率方程

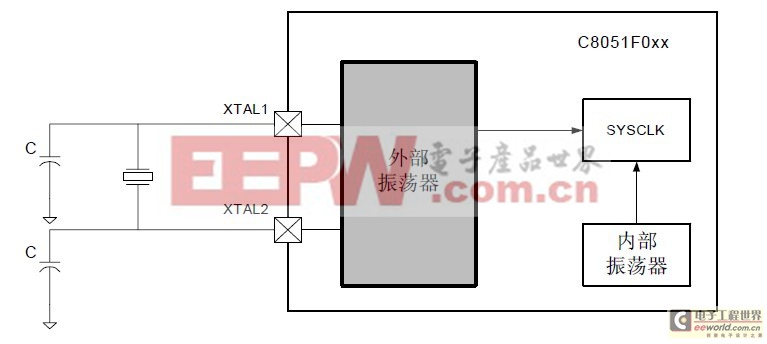

C8051Fxxx系列器件的系统时钟可以来自内部振荡器或一个外部时钟源。外部源可以是一个CMOS时钟、RC电路、电容、或晶体振荡器。内部振荡器可提供四个时钟频率:2、4、8 和16 MHz 很多不同的频率可以通过使用外部振荡器得到。为了节省功耗,设计者必须知道给定应用所需要的最高SYSCLK频率和精度。一个设计可能需要一个在器件全部工作时间内保持不变的SYSCLK频率。在这种情况下,设计者将选择满足要求的最低频率,采用消耗最低功率的振荡器配置。典型的应用包括串行通信和必须用ADC完成的周期性采样。

某些操作可能要求高速度,但只是在很短的,断续的时间间隔内 这种情况在某些时候被称为"猝发"操作

在C8051Fxxx中,SYSCLK频率可在任何时刻改变,因此器件平时可工作在较低的频率 直到某个需要高速操作的条件发生。

切换系统时钟源的两个例子是:(1)内部振荡器/外部晶体配置,(2)外部晶体/RC振荡器配置。如果器件偶尔进行高速数据转换,并使用一个实时时钟为数据提供时间戳,则一个内部振荡器和外

部晶体的组合将是最理想的,在采样操作期间应使用高速内部振荡器。采样结束后,使用一个外部32kHz晶体以维持实时时钟。一旦重新需要高速操作,器件将切换到内部振荡器(见图1)。在应用笔记 "AN008 - 实现一个实时时钟"中给出了这种操作过程的一个例子。

图1. 内部振荡器和外部晶体源配置

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 电源SOC:或许好用的“疯狂”创意(07-24)

- 实现智能太阳能管理的微型逆变器应运而生(05-06)