PLL时钟发生器XC25BS7简介

时间:07-28

来源:互联网

点击:

XC25BS7系列是内置分频, 倍频电路, 在整个频率范围内保持低消耗电流, 具有超小型封装的PLL时钟发生器IC。输入端分频比(M), 输出端分频比(N)的值均可以在1~256范围内通过激光微调方式自由选择。输出时钟(fQ0)的频率等于标准时钟输入频率乘以N/M的比值(即fQ0=fCLKin×N/M)。时钟输出的频率范围为:1MHz~100MHz。时钟输入频率的范围为:32kHz~36MHz。当CE端子输入低电平时,整个芯片停止工作,此时芯片的消耗电流会低于10uA。待机时输出为高阻抗。本产品提供部分客户定制品,有需要时请提供详细的规格要求(输入, 输出频率, 工作电压等)向本公司的各分公司咨询。即使在本产品的规定规格范围内,请注意有些临界范围的频率的设定可能是无法实现的。

特点:

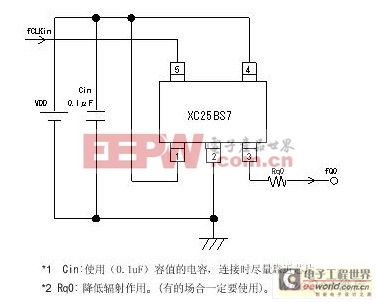

电路框图:

- 一种准确地预测由泄漏电流引起的 PLL 基准杂散噪声之简单方法(12-09)

- 基于高电压电荷泵的PLL频率合成器设计(01-15)

- 良好电源设计有利于提升锁相环性能(09-17)

- 基于DDS+PLL技术的高频时钟发生器(08-30)

- 一种X波段频率合成器的设计方案(08-07)

- GSM、WCDMA和LTE应用的高集成度SyncE器件(04-23)