电源设计:注意那些意外谐振响应

您曾经将输入电压接通到您的电源却发现它已经失效了吗?短暂的输入电压上升时间和可产生两倍于输入电源电压的高 Q 谐振电路可能会是问题所在。如果您迅速中断感应元件中的电流便会出现类似问题。会出现这类问题的一些情况包括热插拔电路或者试图开放输入向电磁干扰 (EMI) 滤波器时。

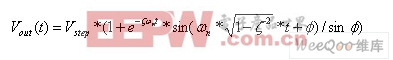

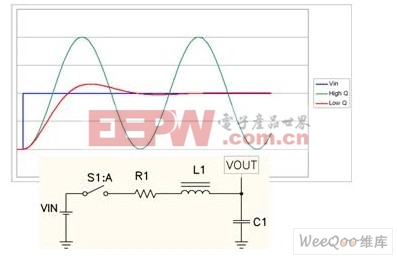

图 1 显示了带开关输入的简化滤波器示意图。电路的电感可以为有意的也可以是偶然发生的,例如:以太网供电 (PoE) 系统的长通电线路。该图还显示了步进的输入电压波形,以及阻尼系数小于 1 时的生成输出电压。(大于 1 的阻尼系数没有过冲。)更低阻尼系数的响应形式如下:

(方程式 1)

(方程式 1)

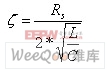

其中: 为斜率,其也等于 1/(2*Q)。

为斜率,其也等于 1/(2*Q)。

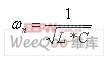

为固有频率,由电感和电容设置

为固有频率,由电感和电容设置

为

为 的反余弦

的反余弦

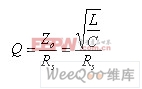

得到串联谐振电路以后,您会很容易地找到 Q,其就是特性阻抗除以串联电阻,即:

(方程式 2)

(方程式 2)

图 1 滤波器响应可导致会损坏下游电子元件的过电压

高 Q(低阻尼)系统为无阻尼,而滤波器输出电压可振铃至两倍输入源 (Vin)。低 Q 系统会限制峰值振铃电压。

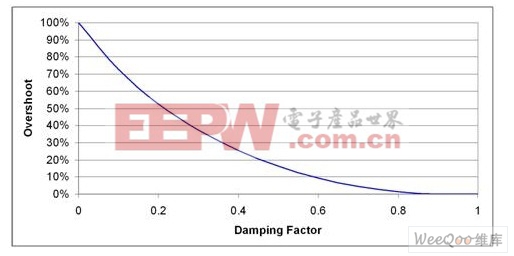

图 2 显示了过冲百分比,其为阻尼比率的函数。使用 0.4(1.25 Q)阻尼比率可将振铃电压限定到源电压的 130%。由于阻尼电阻的额外损耗或将一个电阻与电容串联产生的滤波损耗可能是不可接受的,因此这样做或许并不切实际。如果您的设计不能容忍这些损耗,那么您需要添加一些额外的组件。例如,利用串联电阻以及同滤波器电容 (C1) 并联的电容器可以进一步阻尼电路。您也可以使用热插拔电路来限制滤波器的峰值电流;或者您可以将一个二极管同电感器并联,以提供低阻抗电容充电。

事情并非如看起来那样糟糕。电感器的电流会令其饱和,同时电容充电可以通过比预计更低的串联电感进行。如果电感饱和,则滤波器特性阻抗会像 Q 一样下降,从而减少过冲。要检验在高 Q 系统中其是否会出现这种情况,请利用电压阶跃除以系统特性阻抗来计算峰值电流。之后,请参阅电感产品说明书确定其是否会饱和。

图 2 增加阻尼比率(降低 Q)来减少过冲

总之,阶跃输入电压带来的滤波器振铃可导致对下游电子元件有破坏性影响的电压。特别是如 PoE 的系统,在使用低损耗陶瓷电容和一些不饱和的电感时它们往往为高 Q,则上述电压便成为问题。如果电压达到不可接受的水平,则这些系统会需要更多的阻尼、电流限制或者一种替代充电方法。下面将介绍一种确定您是否存在问题的简单过程:

1)决定您的系统是否经受低阻抗的电压阶跃,然后确定其上升时间。该电压阶跃可以是一个开关或者热插拔连接。

2)估算充电电感和滤波器电容。线缆电感可估算为 15 nH/英寸。

3)确定充电通路的总电阻,包括电感、线缆和连接器电阻,以及电容 ESR。

4)计算谐振频率 ,确定输入上升时间是否大大短于固有滤波器响应。

,确定输入上升时间是否大大短于固有滤波器响应。

5)计算阻尼系数 ,并参考图 2 来确定过冲。

,并参考图 2 来确定过冲。

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)

- 电源设计必看:开关电源设计经典问答(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流--第 2 部分(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流-第 1 部分(12-09)

- 电源设计控制的利弊权衡(12-09)