新型降压稳压器拓扑在宽输入、高用电量负载中的应用

摘要:本文介绍了一种“零电压开关(ZVS)降压”的新型降压稳压器拓扑,说明了其给系统带来的优势和其在Picor Cool-Power ZVS降压稳压器系列产品中的集成。

概述

在当今电子系统应用中,需要更高的功率密度、效率、功率输出的能力以及宽输入及转换比,但是在高输入电压或更高频率的宽工作范围时,传统的硬开关会带来相当大的损耗。对于硬开关拓扑而言,它面临着3个重大挑战:

1. 硬开关:在高电平端主开关上有高电压时,同时流过大电流将产生与频率和电压相关的开关损耗,它是宽动态范围下工作的直接障碍。具有更好的开关速度优点的下一代MOSFET技术应可允许更快的开关。更快的开关切换也具有自身的问题:硬开关(即使是更快的开关)通常带来开关节点上的尖峰和振铃,而且还必须克服电磁干扰(EMI)和栅极驱动损毁。当输入电压和输入频率较高时,这些问题也更加严重,因此,在需要更高电压或更高频率的宽工作范围时,高速开关不具备什么吸引力。

2. 体二极管的导通:同步体二极管的导通不仅不利于高效率,而且限制可能达到的开关频率。在高电平端开关开启之前且同步MOSFET关闭之后,这些同步体二极管通常具有一定的导通时间。

3. 栅极驱动损耗:在高频率开关MOSFET时将带来更高的栅极驱动损耗。

本文介绍一种“零电压开关(ZVS)降压”的新型降压稳压器拓扑,并说明如何把这些拓扑集成在Picor Cool-Power ZVS降压稳压器系列产品内。新型零电压开关(ZVS)降压稳压器的仿真模型,说明这种新型的零电压开关拓扑是如何通过减少上述3个挑战带来的影响,来实现更高的功率密度、效率、功率输出的能力以及宽输入及转换比。在介绍工作原理的同时,还将介绍零电压开关(ZVS) 降压拓扑带来的诸多益处。

传统仿真模型

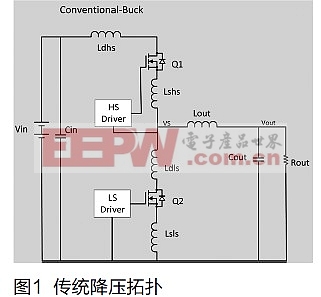

图1给出了典型的传统降压稳压器拓扑图以及相关的寄生电感,包括MOSFET和/或印制电路板走线本身的寄生电感。为了图示说明本拓扑在较高频率应用时的限制因素,我们利用同类最佳MOSFET(以及制造商的SPICE模型)建立一个仿真模型。

假定这个转换器设计将36V输入电压降低至12V,满载电流是 8A。此仿真模型工作在650kHz时采用1个2mH电感,工作在1.3MHz时采用1个1mH电感。MOSFET导通电阻是10 mΩ。对于4个寄生电感,源端寄生电感Lshs设定为 300 pH;其他电感值设定为100 pH。这样做是基于与电源系统级封装(PSiP)电源设计概念相关的封装及布局技术。高电平端栅极驱动器使用4Ω源电阻来实现最小振铃,并使用1Ω灌电阻来加快关闭速度;对于低电平端驱动器,在两种情况下均使用1Ω源电阻和灌电阻。

- 精确度与功率相遇,RefulatorTM是解决之道(05-26)

- 预稳压器设计保护高压电源免生相位故障(03-27)

- 如何采用COT稳压器动态控制输出电压(12-09)

- 线性稳压器的短路保护电路设计(12-09)

- 稳压器常见故障及稳压器维护(12-09)

- 稳压器怎么选购(12-09)