改进的解耦双同步坐标系锁相环的设计与实现

摘要:微网中的电压可能会存在较大的谐波和不平衡,因此要求锁相环(PLL)能够迅速、准确地确定电网正序电压的相位。提出的改进型解耦双同步坐标系PLL通过在q轴加入6次谐波的陷波器,可抑制电网中的5次负序电压和7次正序电压对锁相的影响。锁相程序在相位变化较大时改变正弦表的指针,在相位或频率变化较小时调节DSP周期寄存器。实验证明了该锁相方法的有效性。

关键词:锁相环;双同步坐标系;解耦陷波器

1 引言

在微网中,由于电压可能会存在较大的不平衡和低频谐波电压,因此对于并网逆变器而言,能够准确地获取电网的基波正序电压就尤为重要。文献对常规的d—q变换进行了分析。该变换在电网电压完全对称且没有谐波的情况下能够准确地获取电网电压的相位。当电压存在不平衡或谐波时,锁相得到的相位就会存在误差和波动。降低系统带宽可抑制高频谐波,但减慢了PLL的响应速度,反之亦然。

文献提出在锁相回路中加入巴特沃斯低通滤波器的方法,通过低通滤波器来抑制锁相回路中的低频谐波分量,其仿真和实验证明该方法能显著提高在电网不平衡和存在谐波时的锁相精度。文献先对各相电压进行锁相,然后再采用正负序分离的方法,获得电网电压中的正序分量,最后再采用常规的d—q锁相。该锁相方法能够消除电网电压不平衡造成的影响,并且对谐波电压具有较好的抑制能力。文献提出采用解耦双同步坐标系的方法同时对电网中的正负序电压进行提取,然后将正负序电压进行解耦,可以很好地抑制电网中的负序电压。

在上述基础上,在此提出通过在正序q轴锁相回路中加入300 Hz陷波器的方法抑制电网电压中存在的5次负序电压和7次正序电压对锁相的影响。锁相程序针对较大的相位变化采取改变正弦表指针的方法,针对较小的相位或频率变化采取调节DSP周期寄存器的方法。该实现方法能更好地兼顾锁相的动态性和精确性。

2 改进的解耦双同步坐标系PLL

2.1 解耦双同步坐标系模型

电网电压的表达式为:

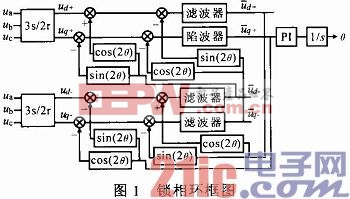

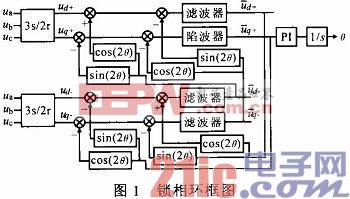

式(4)反映了正负序电压之间的耦合关系:负序d,q分量以一个2倍频分量耦合到正序分量中;正序d,q分量也以一个2倍频分量祸合到负序中。通过式(4)可解耦得到正负序电压中的直流分量,从而抑制电网不平衡对锁相造成的影响。改进的基于解耦双同步坐标系PLL的框图见图1。

2.2 6次陷波器的设计

模拟陷波器的传递函数为:

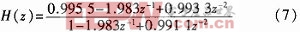

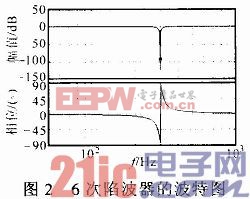

由文献可知,当谐振频率为300 Hz,谐振点3 dB带宽为30 Hz,可得到对应的数字陷波器的传递函数为:

陷波器的波特图如图2所示。由图可见,该陷波器能够很好地滤除300 Hz的谐波。

电网电压通过LV28-P芯片进行检测,通过调理电路和电平抬升电路后将采样得到的电网电压转换到0~3.3V范围内.然后送入DSP2407。

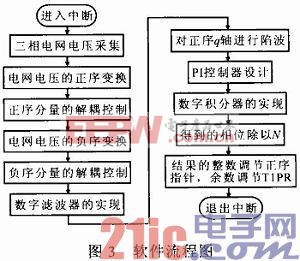

PLL的软件流程框图如图3所示。图3仅显示了中断部分的流程图。在DSP中,数字积分得到的相位先转换成正弦表对应的指针。由于在转换过程中得到的指针可能不是一个整数,而取指针时只能取整数,因此会使相位存在一定误差。对于小数部分,在此采用其来调节DSP的周期寄存器,使锁相精度能够有很大提高。

4 实验结果

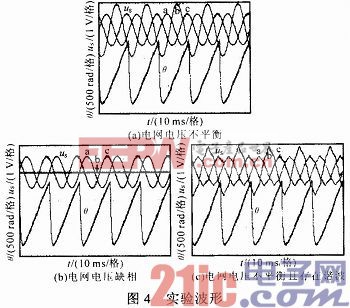

图4a为电网电压不平衡时的锁相波形。图4b为电网电压b相缺相时的锁相波形。图4c为电网电压存在谐波及不平衡时的锁相波形。由图4a,b可见,在电网电压存在严重不平衡甚至是缺相的情况下,该PLL都能很好地锁定电网正序电压的相位,其上升沿基本无纹波。由图4c可见,在电网中存在大量谐波且不平衡的情况下,锁相得到的相位仍能很好地跟踪电网正序电压的相位。

锁相环技术在微网中应用广泛且非常重要。针对微网中可能存在的低次电压谐波和电网不平衡现象,在此提出的基于解耦双同步坐标系的锁相环通过在正序q轴的锁相回路中加入6次陷波器,可很好地抑制电网中的5次负序电压和7次正序电压对锁相环的影响。在此搭建了以DSP 2407为核心的锁相系统,通过实验证明了该锁相环理论分析的正确性和有效性。

- 基于TMS320F28335的微网锁相环的设计方案探讨(12-07)

- 锁相环在频率调制与解调电路中的应用(03-15)

- 鉴频鉴相器的指标对锁相环(PLL)死区及抖动性能的影响(12-07)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)