一种低电压低静态电流LDO的电路设计(二)

2 电路设计与实现

本文所提的低电压、低静态电流的精简结构的LDO如图2所示。LDO的输出级是一个A类共源级电路,包括PMOS功率管M1,三极管Q1、Q2,电阻R1,R2,R3,Resr和输出负载补偿电容C1.功率管M1有非常大的宽长比来驱动比较大的负载电流。因此M1的沟长选取最小的值,达到尽可能小的寄身电容和尺寸面积。为了获取好的暂态输出特性以及环路稳定,输出补偿电容取5 μF.带隙基准电路包括三极管Q1,Q2,Q3和电阻R1,R2,R3.选取Q2的射级面积为Q1和Q3的射级面积8倍,这是Q2面积和R2阻值折中结果。三极管Q3和晶体管M6构成一个共集电极的电路,为环路提供高增益。缓冲级包括晶体管M2,M3和M4.因为NMOS源跟随器,在低负载情况下并不能完全关断功率管,PMOS源跟随器并不适合本电路的1.35低电压环境,所以选用了二极管连结的PMOS负载共源级电路作为缓冲级。这种结构不仅获得低的输出阻抗,同时达到180°的相位偏移,使整个闭环环路构成一个负反馈。M3作用是在低负载电流的情况是为M4提供一些偏置电流,否则可能出现M4的栅源电压过低,导致三极管Q3进入饱和状态,降低Q3的电流增益,影响带隙基准电压的精确度。通过Q4和M7构成的偏置电路,使得三极管Q1,Q3有相等的集电极电流。晶体管M5,M8和M9构成LDO的启动电路。在刚有电压输入情况下,M8和M9构成一个反相器输出一个低电压信号,使M5导通来启动整个电路。

3 电路仿真结果

基于CSMC 0.5 μm 双阱CMOS 工艺仿真模型,采用Cadence仿真软件对精简结构LDO进行了三个工艺角(tt,ff,ss)下仿真验证。这个系统设计指标的是让LDO驱动最大30 mA的负载电流,同时保持输出电压稳定在1.14 V,输入电压最小为1.35 V.LDO 的温漂曲线如图3所示。

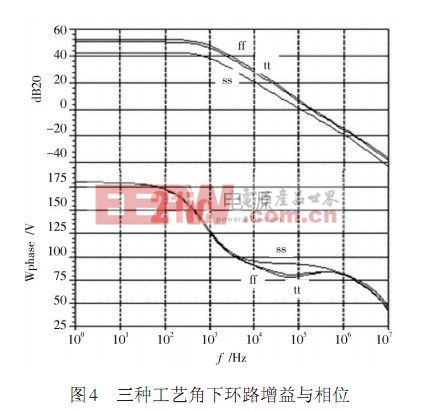

通过采用补偿电容外接串联电阻的方法,创造一个左半平面的零点来补偿一个非主极点,让电路获得比较好的环路相位裕度,在三个工艺角下,相位裕度都能达到70°(见图4)。

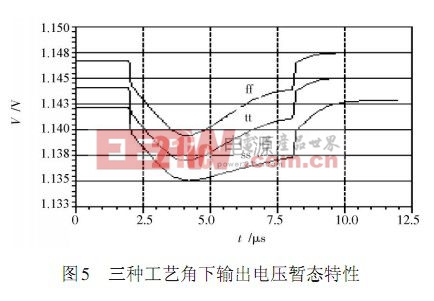

暂态输出电压变化如图5所示,当负载电流从0~30 mA瞬态变化时,输出电压变化最大仅为9 mV.

4 结语

本文给出了一种低电压1.14 V、低静态电流1.7 μA 的LDO,通过将带隙基准电压源与误差放大器合二为一获得精简结构的LDO.

因此实现了低静态电流消耗,同时获得较好的暂态输出电压性能,最大暂态电压变化仅为9 mV.

驱动 相关文章:

- 嵌入式碟式太阳能热发电控制器研制与应用(06-28)

- LED照明驱动技术的创新发展(上)(03-20)

- 差分运算放大器驱动器实现高分辨率ADC输入过压保护(03-23)

- 更严格的法规及日益增加的消费者期望 对白家电行业提出电机驱动新挑战(03-21)

- 用集成式8开关无闪烁驱动器控制矩阵式LED前灯中的单个LED(下)(03-24)

- 基于1602液晶电压驱动器应用于proteus仿真(12-12)