基于FPGA的音乐硬件演奏电路设计与实现

3 系统的方案实现

3.1 各模块仿真及描述

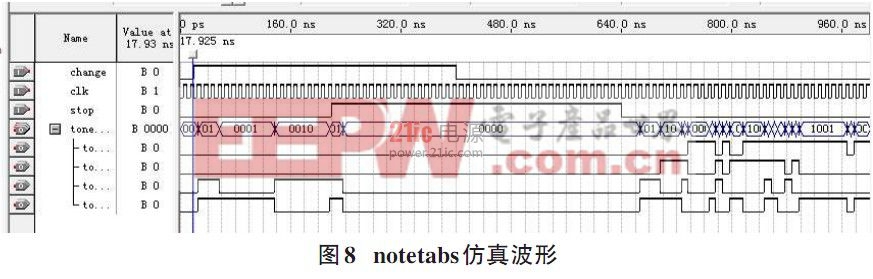

notetabs作为音符rom的地址发生器,此模块中设置了一个8位2进制计数器,频率为4hz,即为4个音符一秒时间四四拍的4分音符。notetabs计数器计数器按4hz时钟频率做加法计数,当stop为高电平时停止加法运算,而当change可设置rom中数据的跳转,rom通过toneindex[30]端口输向tonetaba模块。乐曲就演奏起来了。

由图6 sperkera仿真波形可以看出,当clk输入时钟频率为12mhz时,输出端信号clk输出的频率,随tong信号的不同,输出不同频率的声音信号。

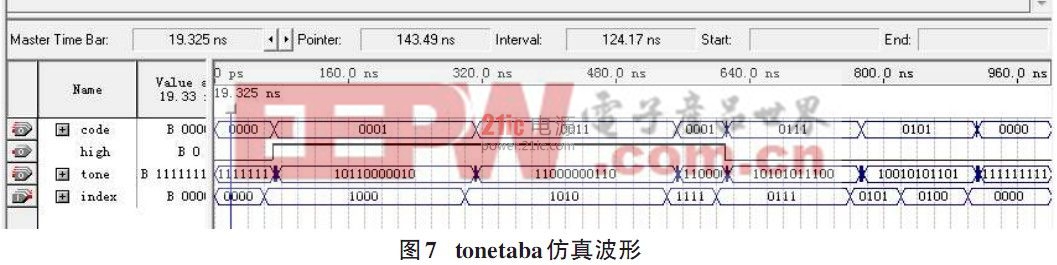

由图7tonetaba信号的仿真波形,可以看出,当输入信号index[30]输入不同信号值,code输出端输出音符的显示,high为音符高位信号,tone大于7时high为高电平。

图8为notetabs仿真波形,当clk输入时钟信号,toneindex[30]端从rom中读入音符数据,当输入端口stop为“1”时,暂停从rom中读入数据,stop为“0”继续读取音符信号,change为高低电平时,模块分别读取rom不同位置的数据。

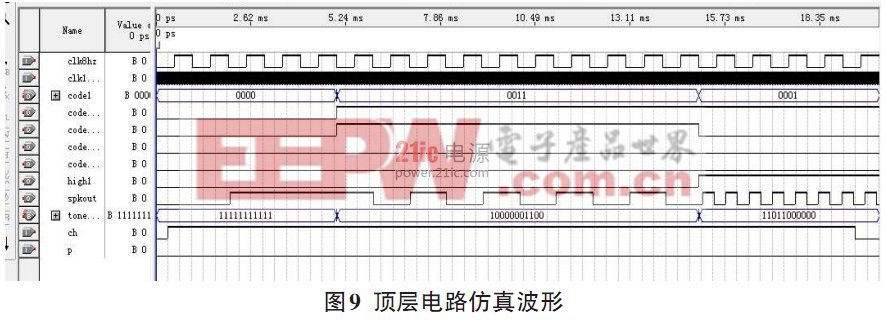

3.2 顶层电路仿真及描述

clk8hz端输入8hz时钟信号,另一个clk12mhz输入12mhz时钟信号,系统将自动从music.mif中读取音符信号,以频率不同输出到spkout,同时输出到显示端口,和高音端口,code1[30],high1.p端口可以是音符暂停输出(高电平时),ch端口控制歌曲间的切换。

4 硬件测试及说明

选择实验电路模式1,将引脚锁定时clk12mhz于clock9连接,短路帽clock接12mhz.clk8hz与clock2连接。发音输出spkout接speaker.简谱码输出code1由数码管5显示,high高8度指示由发光管d5指示,p与按键d16连接,ch与的15连接。最后向目标芯片下载适配后的sof逻辑设计文件。

5 结论

本次设计在EDA开发工具QuartusII平台上,应用语言层次化和模块化的设计方法,通过音符编码的设计思想,预先定制乐曲,在此基础上设计了一个乐曲硬件演奏电路,经过对整体进行模块化分析、编程、综合、仿真及最终下载,完整实现简易音乐器的播放功能。

通过学生自己手动完成简单的数字器件的设计,在加强以传统电子设计方法为基础的工程设计训练的同时,使学生能够更快地掌握现代电子电路设计自动化的新方法和新手段,提高了学生对基础实验的兴趣。

- IR2110驱动电路的优化设计(03-15)

- 基于CAN总线的低压智能断路器的设计(04-06)

- 基于BCM的有源功率因数校正电路的实现(03-12)

- 智能型的铅酸蓄电池管理系统(04-29)

- 基于TPS2384的PSE设计与实现(07-12)

- 开关电源输入平波电路的设计与实现(07-23)