一种CPLD自供电系统实现

有一种常见的工业和消费应用,即按一个长间隔(如每分钟一次)对环境条件,如GPS(全球定位系统)位置、电压、温度或光线进行采样的系统。这类系统正越来越多地采用无线和电池供电方式,它每分钟苏醒过来,作一次采样,将数据传输到一个中央数据采集终端,然后再次进入睡眠状态。本设计实例用一片Altera EPM240-T100 CPLD(复杂可编程逻辑器件)中的一小部分,结合一些分立电容、电阻、二极管和MOSFET,通过一个RC定时器电路,自动将一个CPLD系统从完全断电状态唤醒。

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(在系统编程)将代码传送到目标芯片中,实现设计的数字系统。CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。其中MC结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

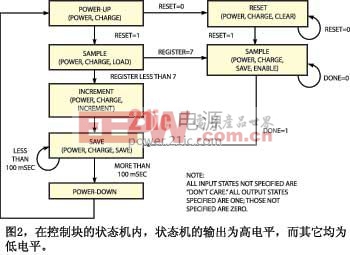

图1是基本的CPLD开/关定时器。Q1是一片IRLML6302 P沟道MOSFET,用作系统的电源控制开关。当门节点为VCC时,R2上拉,连接CPLD和整个系统的电源均被切断,只有RC电路消耗少量电能。CPLD带有一个控制块、一个4.4MHz内部振荡器、一个3位寄存器,以及6个I/O.图2为控制部分的状态机。从掉电到上电的虚线表示时间延迟,该时间延迟在系统断电时由R1与C1构成的RC电路测量。开关S1接通时电路初始化。当S1闭合时,D2将门节点拉低,当门电压低于VCC 0.7V时Q1导通。Q1加电不到200ms后,EPM240-T100工作在上电状态。上电状态将电源节点拉低,将门电压保持在0.7V,在开关打开后使Q1维持导通。

接下来,采样与传输电路开始工作,使done信号为0.当采样与传输完成时,done信号变为1,而控制块进入保存状态。保存状态按照Register 1中的值,将电容C2充电至CN.保存状态激活100ms时间,使输出对10mF电容完全充电。经过100ms后,控制块进入断电状态,停止驱动充电节点与电源节点。R4将电源节点拉高,而R2拉高门节点。

当门节点使VCC-VTQ1达到大约 2.3V时,Q1切断系统的供电。EPM240-T100的所有I/O均处于高阻抗状态,并且不影响门节点或充电节点。充电节点开始于VCC,并在电源关断时开始通过R1放电。一旦充电节点掉落到2.3V,D1拉低门节点。当充电节点达到1.6V 时,门节点为2.3V,Q1 导通。

器件在上电状态上电,但很快转至采样状态。采样状态记录电容C2、C3和C4上的值。这些电容用作非易失存储器,保存以前上电循环的次数。如果C4 ~ C2上采样的Register 1值小于7,则控制块开始递增,而Register 1的值以1为增量增加。然后,控制块再次进入保存状态,C2 ~C4充电到一个新的二进制值001.器件再次断电。在第8次上电循环,或上电后大约80s,控制块转为使能状态,因而开始一个新的采样与传输顺序。这个过程每80s重复一次。你可以调整C1和R1改变Register1的大小和使能循环之间的计数,就可以改变这个80s的周期。由于80s周期包含8个较小的上电采样、测试与断电循环,供电的占空周期小于3%,因此,这种方案将电池寿命增加了33倍。

- 模块电源的热测试步骤(12-09)

- 工程师必知:如何设计和测试场效晶体管的集成电路?(12-09)

- 电子工程师 你该知道的电源测试项目(12-09)

- 第一次设计和测试反激式电源(12-09)

- 在通用自动测试仪上实现SPI 存储器测试的方法研究(12-09)

- 一种继电器测试数据查询系统的实现(12-09)