双层加载电路板屏蔽腔屏蔽效能研究(二)

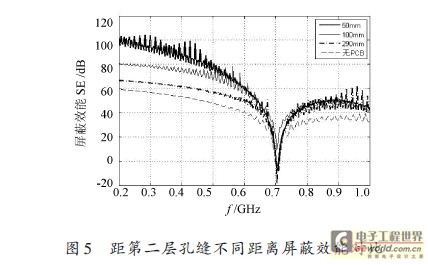

2.2 介质板与第二层孔缝之间的距离对屏蔽效能的影响

介质板尺寸不变为300 mm×120 mm×1 mm.内层孔到加载PCB 板的距离q 变化。在这里q 分别取50 mm,100 mm 和290 mm,最后和没有PCB 板的情况做对比。

由图5 可知,在给定频率范围内,介质板离第二层孔缝越远,屏蔽效能越低。当介质板离第二层孔缝50 mm的时候,大部分耦合场发生反射,耦合出腔体,因此第二层腔体中心场强是最小的,屏蔽效能是最大的,随着距离的增大,腔体中心场强也逐渐增大,当增加到290 mm的时候,腔体中心场强达到最大值,与无介质板时的场强接近,屏蔽效能也与无介质板时接近。

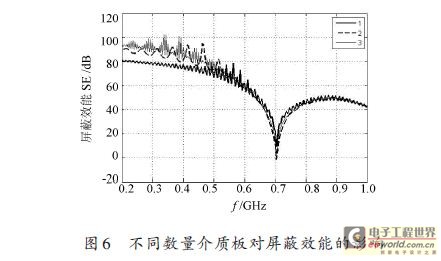

2.3 介质板数量对屏蔽效能的影响

介质板大小均为300 mm×120 mm×1 mm,当只有一块介质板的时候,放置在距第二层孔缝100 mm 的地方,即图1 中q=100 mm 的地方;当有两块介质板的时候,放置在距离第二层孔缝50 mm 和100 mm 的地方,即图1 中q=50 mm 和q=100 mm 的地方,当有三块介质板的时候,放置在距离第二层孔缝50 mm,100 mm 和150 mm 的地方,即图1 中q=50 mm,q=100 mm 和q=150 mm的地方。仿真结果如图6所示。

由图6 可以看出,随着介质板数量的增加,腔体中心位置的屏蔽效能有所增加。

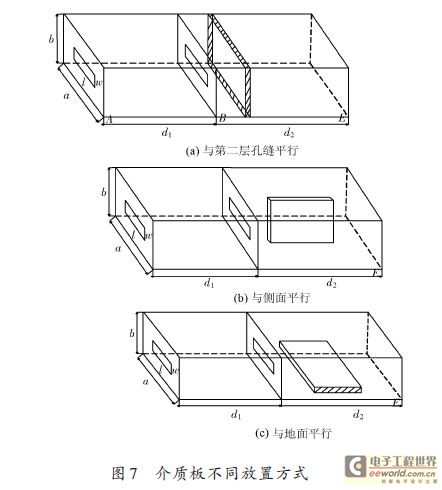

2.4 介质板不同放置方式对屏蔽效能的影响

介质板大小不变,以下面三种不同的方式放置:与第二层孔缝平行,放置在距离地二层孔缝100 mm的位置;与侧面平行,放置在垂直于孔缝长边中央的位置;与地面平行,放置在垂直于孔缝短边中央的位置。三种放置方式如图7所示。

三种情况仿真结果如图8所示。

由图8可知,介质板平行与地面放置时屏蔽效能最差,其他两种放置方式对屏蔽效能影响不大。

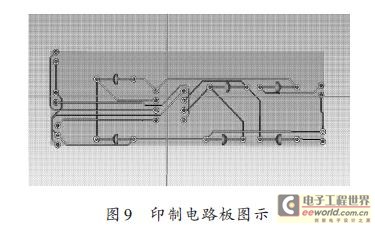

3 加载集成运算放大电路板对屏蔽效能的影响

实际的印制电路板和等效的宏观介质板还是存在一定的差异,在这里,将宏观介质板替换为集成运算放大电路板,如图9所示。

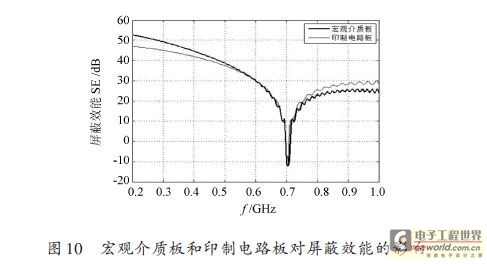

对比介质板和电路板在屏蔽腔中对屏蔽效能的影响,设置介质板大小与电路板相同,均为75.59 mm×25.69 mm×0.711 2 mm,均将模型放置在屏蔽腔后腔中心距z 轴原点-99.288 8 mm 的位置,此处介质板为前面提到的电导率为σ = 0.22 S - m-1 介电常数为εr = 2.65 的宏观介质板,印制电路板采用图9所示的加载集成运算放大电路的电路板。运用CST,将电路板的PCB模型导入到CST的微波工作室中,经过仿真后,其结果如图10所示。

对比介质板和电路板在屏蔽腔中对屏蔽效能的影响,设置介质板大小与电路板相同,均为75.59 mm×25.69 mm×0.711 2 mm,均将模型放置在屏蔽腔后腔中心距z 轴原点-99.288 8 mm 的位置,此处介质板为前面提到的电导率为σ = 0.22 S - m-1 介电常数为εr = 2.65 的宏观介质板,印制电路板采用图9所示的加载集成运算放大电路的电路板。运用CST,将电路板的PCB模型导入到CST的微波工作室中,经过仿真后,其结果如图10所示。

由图10 可知,在大小、厚度、放置位置相同的情况下,宏观介质板和印制电路板得到的屏蔽效能相差不大,即用宏观介质板等效替代印制电路板误差较小。

加载印制电路板后腔体屏蔽效能主要表现在电路板表面电场强度的变化和表面电流的不同,通过CST仿真,得到下述结果。

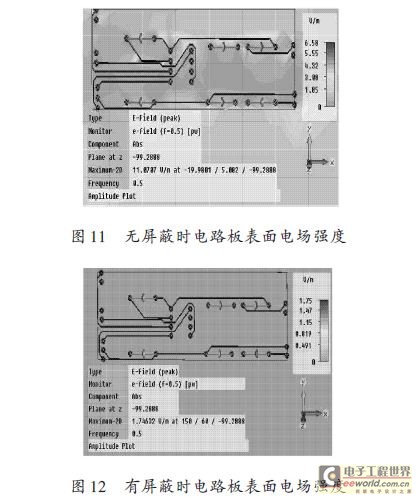

3.1 电路板表面电场

从由图11 和图12 可知,无屏蔽时最大场强为11.070 7 V·m-1 ,有屏蔽时最大场强为0.164 V·m-1 ,可见屏蔽腔对电路板起到了良好的屏蔽效果。并且相隔较近的导线之间容易引起高场强,如果没有屏蔽,将会引起电路板的正常工作,严重时引起损坏。

3.2 电路板表面电流

在图13 中,无屏蔽时电路板表面电流最大值为0.014 93 A·m-1 ,图14中,有屏蔽时电路板表面电流最大值为2.091 8e - 005 A·m-1 ,明显比无屏蔽时减小许多,说明屏蔽腔对电路板起到了良好的屏蔽效果。

4 结语

本文用传输线等效模型推出双层加载电路板矩形腔体屏蔽效能的计算公式,通过仿真验证了公式的正确性,并得出结论:在给定频率范围内,介质板越大,腔体屏蔽效能越高;介质板离第二层孔缝越近,屏蔽效能越高;介质板数量越多,屏蔽效能越高;介质板平行与地面放置时屏蔽效能最差,其他两种放置方式对屏蔽效能影响差别不大。通过以上结论,在设计机壳时,可以通过对内部电路板的合理布局提高系统的屏蔽效能,同时,腔体内电路的响应频率应当避开腔体的谐振频率。在本文中,为了更加贴合实际应用,将等效介质板替换为加载集成运算放大电路的印制电路板模型,通过CST仿真,验证了宏观介质板等效代替印制电路板的有效性和相似性,并且验证了屏蔽腔体对内部电路板良好的屏蔽效果以及屏蔽腔体对电路板功能的影响。

双层加载电路板屏蔽 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)