适用于小功率电机驱动的MOSFET逆变模块设计

数。因此,Vth的变化范围对确定最坏情况的延迟时间和空载时间有很大作用。在满足这些要求的同时,输出电压变化 (dV/dt) 应当小,以降低电磁干扰。图1(a)和(b)所示的开关特性是满足如下条件时测试的结果:dV/dt=2kV/ms,空载时间=1.0ms,导通延迟时间=2.5ms (延迟时间是在最坏的运行情况下,并考虑栅极电阻和其它器件参数的离差后,从输入信号脉冲中心到建立电流稳定所需的时间)。我们已通过适当选择栅极导通电阻和阈值电压达到了这些条件。

除了这些可预先确定的特性外,用户还可控制模块的开关速度。象其它SPM系列一样,本文介绍的这种模块在高压侧MOSFET上提供开放源极输入端,允许用户加入自己的阻抗单元来控制高压侧MOSFET的开关速度,从而在开关损耗与电磁干扰之间作出最佳平衡。

应用方面的考虑

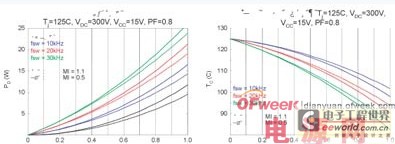

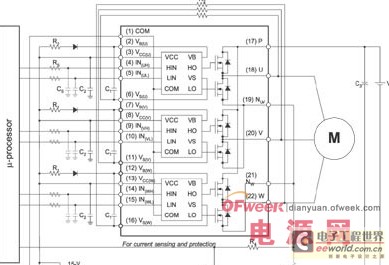

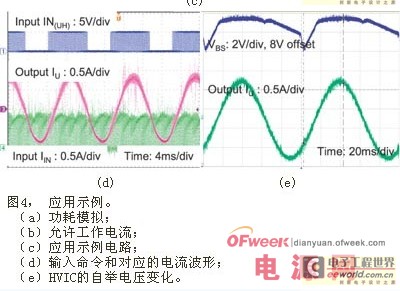

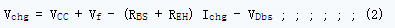

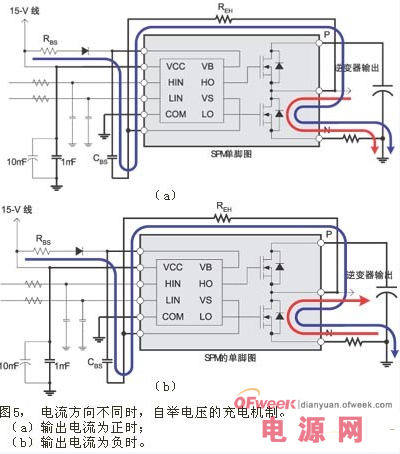

图4给出了本模块的一个应用示例。在图4(a)和(b) 的模拟中,假设结区温度Tj保持为125℃;该温度为本模块的最大工作结区温度。通过这项模拟,肯定当模块外壳温度控制在100℃并采用空间向量调制 (SVPWM) 时,输出功率可大于Pout=100W,并允许Pd=16W的功率损耗。根据这些信息,我们利用一台130W BLDC电机(正弦反电动势) 和图4(c)所示的电路,对模块的额定功率进行验证实验。实验中采用的散热片有效表面积约为100cm2。采用该散热片后,模块在20kHz SVPWM下可向电机输出150W的功率;热功耗为12W。而此时模块的外壳温度为86℃,MOSFET结区温度为104℃,环境温度27℃。在同样条件下采用图4(d)所示的非连续PWM时,由于有效开关频率降低,模块的功耗可达到8W,而逆变器效率可达到95%。此时,模块的外壳温度为62℃,结区温度为82℃(已考虑电机铁芯的损耗),逆变器的损耗为整个系统功耗的27%。MOSFET逆变器的另一个优点是图4(e)所示的自举电压(阴极输出电压)。从图4(e)可以看出,电机的工作频率为10Hz。图中画出了自举电压和逆变器输出电流。当电流为正时,自举电压VBS维持在VCC=15V附近,但当电流为负时,VBS就下降到接近10V。这是由于不同电流方向采用不同的充电机制所造成 (参见图5)。当输出电流为正时,电流要么流经高压侧MOSFET,要么流经低压侧体二极管。在这种情况下,当低压侧体二极管导通时,将对自举电容CBS充电 (参见图5(a))。此时,对CBS的充电电压可由公式(2)表示。

其中,VDbs是跨过阴极输出二极管的电压。如果充电电流小,Vchg仅仅提高Vf -VDbs;该差值最多为1V,它反映如图1(b)所示的低压侧体二极管上的压降。但当输出电流为负时,充电电压将由公式(3)表示。

Vchg = VCC + Rds(on)Io - (RBS + REH) Ichg - VDbs ; ; ; ; ; (3)

这里,Io为输出电流。如果电流是负的,充电电压Vchg将随输出电流大幅下降,这是低压侧MOSFET作为主用开关时MOSFET的正向压降所致。这个自举电压是高压侧MOSFET的栅极驱动电源,且仅在电流为正时有意义。当电流为正时,由于MOSFET的Vf小,自举电压变化不大,因而无需大的自举电容。只需用较小的自举电容就可维持所需的自举电压,这个电压仅在电流为正时用来维持HVIC的待机电流。在过调高速电机运行情况下,高压侧MOSFET在输出频率的半个周期内全导通。例如,若采用单脉冲模式 (或6级阶梯波模式) 的PWM进行调制,输出频率为100Hz,则高压侧MOSFET的导通时间可持续5ms。在此期间,不可能一直对自举电容充电,而自举电容的自举电压随HVIC待机电流的变化可按公式(4)计算。

ΔVBS =Δ tIQBS / CBS ; ; ; (4)

这里,IQBS为HVIC的待机电流,并忽略了CBS本身的漏电流。假设最大待机电流为100mA,CBS为1mF,那么,自举电压在5ms内的变化 芕BS也只有0.5V。这意味着,采用1mF的陶瓷电容就足以维持这种MOSFET逆变器在整个运行过程中所需的自举电压。

除了 自举电路问题外,采用HVIC还会引起许多别的问题;尤其当VB电平低于地电平时最为显着。在HVIC中,高压侧栅极单元是用p-n结隔离的,而输入信号要通过额定电压为625V的电平漂移MOSFET传输到高压侧单元。为了降低信号传输期间的功耗,将开关信号转换成置位复位脉冲;该脉冲触发对应电平漂移 MOSFET和高压侧单元中的置位复位(SR)闩锁电路。当VS低于 -5V时,电平漂移MOSFET不能传送触发信号到高压侧逻辑电路。而且,若VB小于0V,VB与逻辑地之间的寄生二极管将会导通;这会产生过量的电流,从而破坏HV

IC。在实际应用中,当负载电流非常大,或有冲击电涌噪声施加在VB或VS端时,VB可能在很短时间内被拉到0V以下。除了对HVIC本身造成破坏外,还会使HVIC出现误操作或闩锁现象。当HVIC出现闩锁时,其行为将不可预测,

小功率电机驱动MOSFE 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)