通过数学计算了解交错ADC的杂散

时间:12-08

来源:互联网

点击:

时间交错ADC时存在的许多不匹配现象。在这些不匹配显像中有一个更为明显的问题:这些不匹配所产生的杂散有多大? 现在,在知道了各种不匹配会引起交错杂散,并且知道杂散在哪里的情况下,工程师该如何知道杂散有多大呢?

首先,先从失调不匹配杂散开始。 两个ADC之间的失调不匹配会在fs/2处产生杂散。 如何知道该杂散有多大呢? 请看看下面的公式1,其中OffsetMismatch表示码数。

公式1

现在,考虑一个双通道器件的两个14位ADC之间的典型失调不匹配。 通常,其标称值约为满量程的0.5%。 这意味着,码数为214的0.5%,即81.92个码。 将该值代入公式1,得到下式:

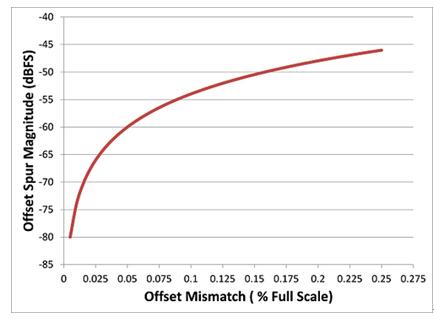

这是一个很有意思的结果! 满量程0.5%的误差看起来不算什么,但它产生的失调杂散却相当大。 当今的多数高速ADC应用无法容忍此类杂散。 交错ADC的无杂散动态范围(SFDR)规格将以它为主。 多数应用要求至少70dBc的SFDR,这意味着杂散过高。 现在看看为了达到或超过70dBc (-71dBFS)水平,杂散应当是多少。 图1给出了失调杂散水平与失调不匹配(单位为满量程的百分比)的关系图。

图1 . Offset Spur vs. Offset Mismatch (Interleaved 14-bit ADCs)

通过此图可以看出, 对于14位转换器,为了满足70dBc (-71dBFS)的典型杂散要求,失调不匹配必须小于满量程的0.025%。 由此可以了解,失调匹配必须达到多么高的精度。 这是非常小的值! 失调必须非常严格地匹配才行。

数学计算AD 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)