基于测试系统的FPGA测试方法研究

1 引言

目前FPGA大多采用基于查找表技术,主要由可编程输入/输出单元(IOB)、可编程逻辑单元(CLB)、可编程布线资源(PI)、配置用的SRAM、BlockRAM和数字延迟锁相环(DLL)等部分组成。对FPGA进行测试要对FPGA内部可能包含的资源进行结构分析,经过一个测试配置(TC)和向量实施(TS)的过程,把FPGA配置为具有特定功能的电路,再从应用级别上对电路进行测试,完成电路的功能及参数测试。

2 FPGA的配置方法

对FPGA进行配置有多种方法可以选择,包括边界扫描配置方法、Xilinx公司专用的SPI/BPI FLASH配置方法、System ACE配置方法、CPLD+第三方FLASH配置方法、系统直接加载配置向量的配置方法。边界扫描方法主要适合在线配置调试用,Xilinx专用Flash配置方法,每次只能在FLASH中存储一段配置码,不适合反复配置测试过程。System ACE方法需要专门的System ACE控制芯片和CF卡,应用比较麻烦。比较适合系统测试的主要是后两种方法。

2.1 测试系统直接配置方法

当采用的测试系统比较高级,比如Teradyne公司的UltraFLEX,该系统测试频率高达500 MHz,测试通道数多达1024个,测试向量深度可达128 M,可以使用系统直接加载二进制配置向量对FPGA进行配置。

能够在同一个操作流程中完成FPGA芯片的多次“配置-测试”过程。该方法操作简单,提高了FPGA芯片的测试效率,能够实现FPGA芯片的产业化测试。

2.2 CPLD+第三方FLASH的配置方法

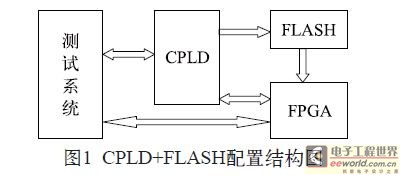

当待测FPGA的配置代码比较大,而测试系统(ATE)向量深度不足时,可以采用 CPLD+第三方FLASH的配置方法,其结构图如图1所示。

其中CPLD的设计是最重要的部分,它所实现的功能模块包括接口模块、控制模块、地址发生器模块。接口模块实现与测试系统的通信,接收测试系统指令并作相应处理,同时将工作状态反馈给测试系统;控制模块提供控制时序命令,操纵整个配置过程;地址发生器模块为读取闪存数据提供数据地址。CPLD内部各功能模块采用硬件描述语言实现。

Flash是配置文件的存储器件,预先将多段16进制格式配置文件烧写进Flash中。FPGA是系统中配置的目标器件。

本方法采用ATE控制CPLD读取FLASH中不同地址范围内的配置代码对FPGA进行配置,再在不掉电的情况下对配置好的FPGA进行功能和参数测试。

3 FPGA配置模式选择与配置码的生成

3.1 FPGA配置模式选择

FPGA的配置模式有多种,而且不同系列FPGA的配置模式有一定的差别,主要的配置模式有:主串模式、从串模式、主并模式、从并模式和边界扫描模式。通过设置三个模式选择管脚M0、M1、M2可以选择不同配置模式。配置模式如表1所示。

用测试系统对FPGA进行测试大部分时间是用在配置上,配置时间根据配置码大小不同可达几毫秒到数十秒。为了提高配置速度,我们对FPGA进行配置选择从并模式,可以最大地节省测试配置时间。以Virtex-II系列FPGA为例,其从并配置模式原理图如图2所示。

3.2 配置码的生成

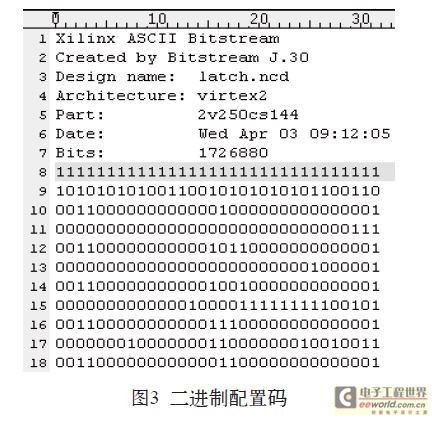

3.2 配置码的生成FPGA配置码要在Xilinx ISE开发环境下编写配置程序,生成所需要的二进制格式配置文件,如图3所示。

图中1~7行属于文件头,需要删除掉,第8~9行就是配置数据开始标志:FFFFFFFF AA995566,后面的都是配置数据。

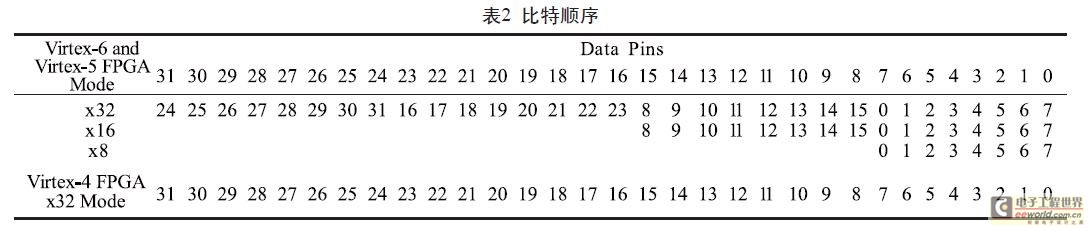

配置文件数据宽度都是32位,还要根据不同系列FPGA的配置数据宽度进行修改。以Virtex-II系列为例,它的从并模式数据宽度是8位,我们需要编写应用程序转化成8位宽的数据。配置数据比特顺序如表2所示,以8位宽数据为例,其D0为最高位。

4 FPGA的配置与测试流程

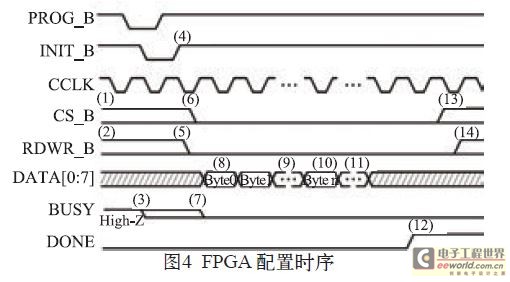

FPGA配置过程主要有四个步骤:清除配置存储器、初始化、配置和启动。以Virtex-II FPGA为例,配置过程的时序要求如图5所示:系统上电后给PROG_B管脚一个低信号,FPGA便开始清除配置存储器,FPGA内部将INIT_B管脚和DONE管脚拉低。当配置存储器清除完毕,INIT_B会变高,之后若CS_B为低有效,就可以传送配置数据对FPGA进行配置,当管脚DONE由低变为高,便标志芯片的配置完成。

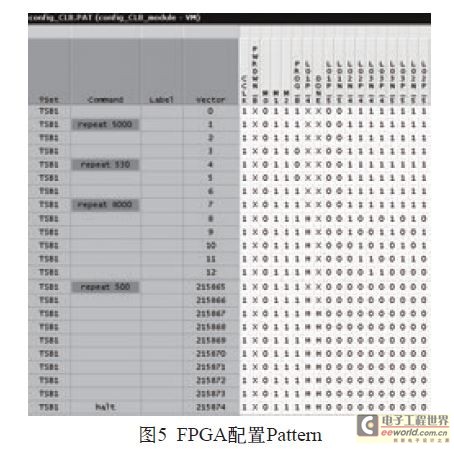

用测试系统对FPGA进行测试可以把配置代码和测试代码分别做成不同的Pattern文件,把配置过程也作为一个功能测试项,这样便可对被测FPGA电路进行反复的配置--测试。配置pattern文件如图5所示。

FPGA配置完毕后,便具有一定的功能,可以像其他电路一样进行功能和参数测试。

5 结论

本文详细介绍了FPGA配置方法、配置模式选择和配置码的生成方法,并以Virtex-II系列FPGAXC2V250为例详细介绍了用测试系统Ultra-FLEX对FPGA的配置与测试过程。 该方法可广泛应用于各种FPGA的测试,具有较强的通用性,对于实现FPGA的产业化测试具有重要意义。

测试系统FPGA测 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)