如何将总谐波失真降至 10% 以下

LED 照明领域普遍关注的问题一直是如何将总谐波失真 (THD) 保持在 10% 以下。电源不但可作为非线性负载,而且还可引出一条包含谐波的失真波形。这些谐波可能会对其它电子系统的工作造成干扰。因此,测量这些谐波的总体影响非常重要。总谐波失真可为我们提供信号 w.r.t. 基波分量中谐波含量的相关信息。更高的 THD 就意味着出现在输入电源端的失真越大或电源质量越低。

因此,我不得不使用 15 W 射灯(绝缘)设计来测试一个设计方法,该设计方案采用针对 7 个串联 LED 配置的TPS92314器件,可通过 150 ~ 265V AC 输入提供 3.1V 正向电压和 0.7A 额定电流。按照下列指示,我在 240V 的 AC 输入电压下实现了 8.7% 的 THD。

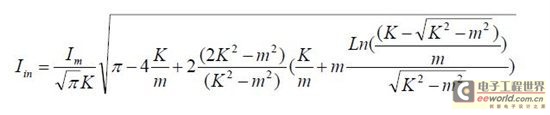

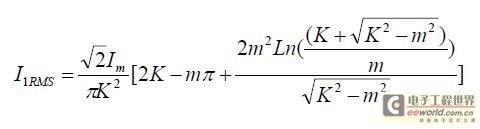

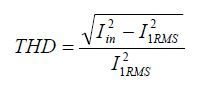

在进行实际实施之前,请查阅本应用手册,了解完成该测试所需的两个重要方程式。

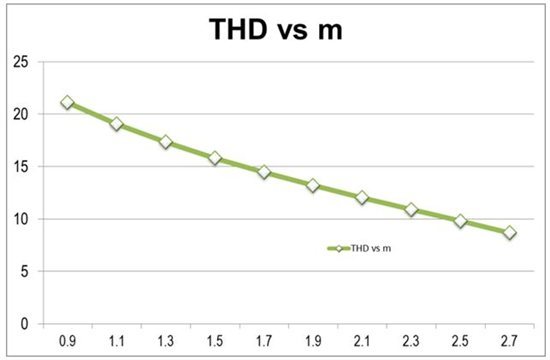

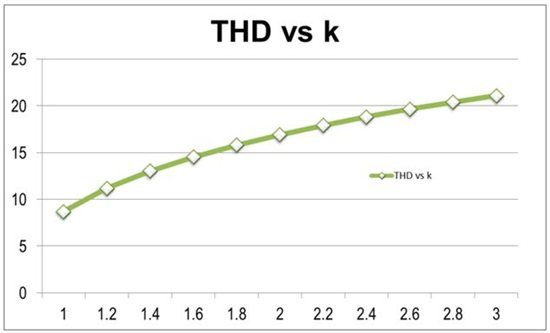

在本例中,k 等于 1.68,我们可通过上述方程绘制出当 k = 1.68 时 THD 与“m”的关系曲线图。

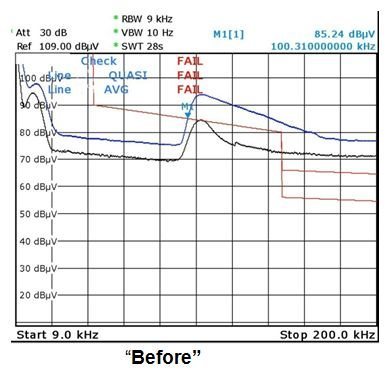

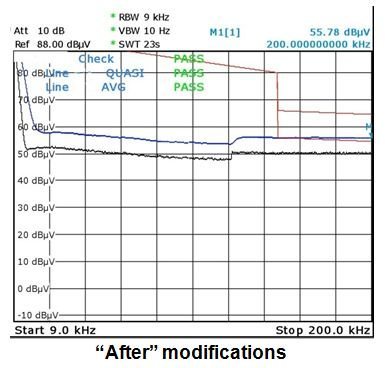

从下图中我们可以看到,当 k 增大时(在 m 因此,重新看一下“m”和“k”的定义,我们就会发现,增大匝数比(n = Np/Ns)及转换器延迟时间,可降低 THD。除这两个参数外,EMI 滤波器设计也可对 THD 的改善起到非常重要的作用。用来降低总谐波失真的三个设计注意事项包括: 通过进行上述改变,我才得以在 240V 的输入电压下实现 8.5% 的 THD 以及 0.98 的 PF,输出电压为 21.8V。在相同设计中的输出端(18.8V 输出)使用六个 LED,我们在 240V 电压下实现了 9% 的 THD。通过 EE1685 磁芯(匝数 180)实现了 80mH 的 EMI 滤波器。主变压器的初级电感为 2mH,峰值主电流约为 0.5A。 本次测试使用的 LED 驱动器是TPS92314,这款一次侧控制离线 LED 驱动器主要用于低成本照明应用(少量外部元件)。它具有恒定导通时间架构,无需复杂的补偿技术就可实现自然功率因数校正。此外,谐振谷值开关也可减少 EMI,提高系统效率。其它优异的特性还包括逐周期一次侧电流限制、VCC 过压保护及欠压锁定、输出 LED 过压保护以及控制器关闭等。 基于TITPS92314的完整原理图如下。 参考资料:

总谐波失真10 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)