输出短路保护的电路设计

时间:12-09

来源:互联网

点击:

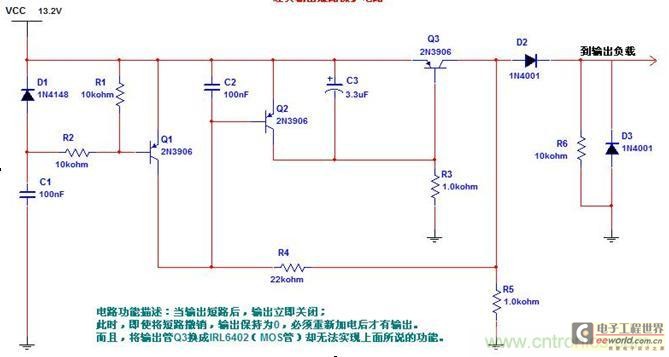

上电:C2 两端电压不能突变,Q2基极电压由VCC开始下降,下降到Q2可以导通(BE结压降取0.7V),这个时间大概是0.12mS。但是同时Q1也在起到阻止Q2导通的作用,Q1导通的时间大概是:5.87mS也就是说 Q2在5.87mS后才会导通,但是同时C3在阻止Q3的导通,阻止时间是0.17mS。

Q3在上电0。17MS后导通,负载得电,Q3 C极电压达到13.3左右,迫使Q2截至,由此可见Q1可以去掉。

短路时,Q3 C极被拉低,Q2导通,形成自锁,迫使Q3截止,Q3截至后面负载没有电压,这时有没有负载已经没有关系了,所以即使拿掉负载也不会有输出。要想拿掉负载后恢复输出,可以在Q3得 C E结上接一个电阻,取1K左右。

输出短路电路设 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)