FPGA验证之功能仿真和时序仿真的区别与方法

这里我们使用一个波形发生器作为例子,来说明如何使用Modelsim对Quartus II生成的IP Core和相应的HDL文件进行功能仿真和时序仿真。这个例子里面使用到了由Quartus II生成的一个片上ROM存储单元。这种存储单元和RAM一样,都是基本的FPGA片上存储单元,在以后的设计里面会经常使用到。

功能仿真

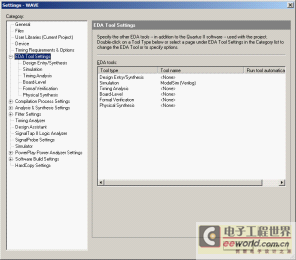

(1)在Quartus II中设置第三方仿真工具,选择“Assignments-Settings-EDA Tool Settings-Simulation”,选择“ModelSim-Verilog”。如图1所示。

图1 EDA工具设置

(2)编译工程。编译带有IP Core的工程文件。

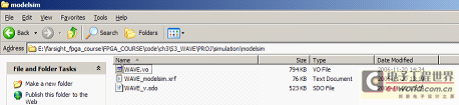

(3)编译完成后会在工程目录下生成“simulation-modelsim”的目录,如图2所示。其中包含了3个文件:“.vo”是仿真网表文件,可以用来代替设计文件;“.xrf”是Quartus编译生成的信息文件;“.sdo”是工程延时信息。

图2 编译生成文件(4)加入仿真库文件。

仿真库的路径为“C:\altera\quartus50\eda\sim_lib”,包含了如下3个仿真库文件。

· 220model.v:带有用户原语类型的Quartus自带的IP核的库文件。

· altera_mf.v:Quartus自带的IP核的库文件。

· cyclone_atoms.v:相应系列的器件库。

在本例中需要添加altera_mf.v,cyclone_atoms.v两个库文件。

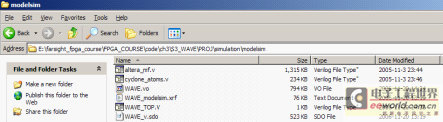

(5)将测试文件粘贴到刚才生成的目录中,如图3所示。

图3 添加测试文件

(7)打开modelsim。

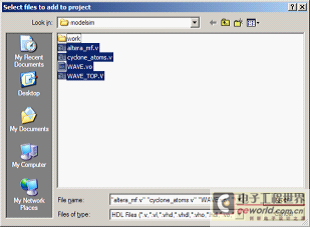

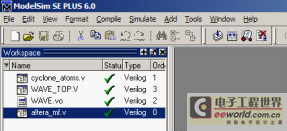

(8)创建工程并添加源文件,如图4所示。

图4 为工程添加源文件(9)编译工程。结合库文件一起进行编译、如图5和6所示。

图5 全部编译前

图6 全部编译后

(10)修改wave.vo文件。将文件中的延时信息注释掉,即:

//initial $sdf_annotate("WAVE_v.sdo");

(11)重新编译wave.vo文件。

时序仿真

(1)将功能仿真第(10)步中对wave.vo文件做的注释改回来,重新进行编译。

(2)重新打开开始仿真对话框,选择顶层模块。

(3)选择“SDF”选项卡。

(4)加入“.sdo”文件,将两个SDF Options都选中。

(5)和功能仿真一样,为波形窗口添加信号,开始进行仿真。

(6)通过波形图,查看时序仿真的延时。

FPGA仿真时序仿 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)