VHDL的QPSK调制解调技术系统的设计与仿真

QPSK调制技术在数字通信调制技术中占有非常重要的地位,将通信技术与FPGA结合是现代通信技术发展的一个必然趋势。QPSK技术具有抗干扰性能强、误码性能好、频谱利用率高等优点,目前广泛应用于数字通信、数字视频广播、数字卫星广播等领域。文中详细介绍了QPSK技术的工作原理,完成QPSK调制、解调的系统设计方案,并通过VHDL语言编写调制解调程序,通过QuartusⅡ软件对模块和程序进行仿真,并通过引脚锁定,下载到FPGA芯片EP1K30TC144-3中,软件仿真和硬件验证结果表明了该设计的正确性和可行性。

1 基于FPGA的QPSK调制解调系统设计

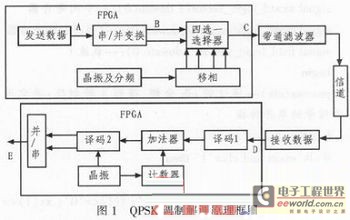

四进制绝对移相键控(QPSK或4PSK)利用载波的四种不同相位来表示数字信息。由于每一种载波相位代表两个比特信息,因此每个四进制码元可用两个二进制码元的组合来表示(常被称为双比特码元),一般用格雷码排列。调制解调的实现原理框图如图1所示。由图1可知,电路主要由分频器和四选一开关等组成,分频器对外部时钟信号进行分频和计数,并输出4路频率相同而相位不同的相干数字载波信号;晶振及分频、移相电路分别送出调相所需的4种不同相位的载波,按照串/并变换器输出双比特码元的不同,逻辑选相电路输出相应相位的载波。四选一开关是在基带信号的控制下,对4路载波信号进行选通,输出数字QPSK信号。但这还不是真正的QPSK信号,需要在FPGA器件外部加一个D/A变换器,将输出转换为模拟信号。

由于QPSK信号可以看作两个载波正交2PSK信号的合成。对QPSK信号的解调可以采用与2PSK信号类似的解调方法进行解调,一般情况下采用相干解调,得到较好的解调效果。2 QPSK数字调制器仿真

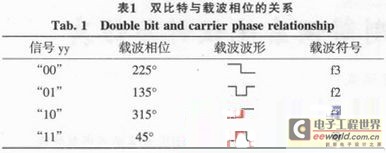

QPSK信号产生的两种方法有相位选择法和正交调制法,在该设计中我们采用相位选择法,具体关系如表1所示。

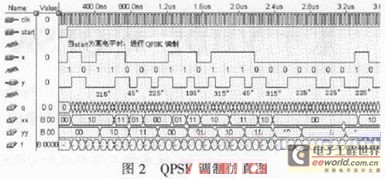

输入时钟信号clk及使能信号start,当start为高电平时才进行QPSK调制,输入基带信号进行串/并变换。基带信号x由一路信号变为两路并行信号,变换后分别为a信号和b信号,则ab信号构成两位并行信号yy,变换后的yy值如表1所示。时钟信号进入八分频计数器q进行分频得到4种不同相位的载波。载波相位为45°、135°、225°、315°的4种载波。四选一开关根据信号yy值,选择载波对应相位进行输出,可得到已调信号Y。如表1所示,当yy值为“0”,选择输出对应的载波f3;当yy值为“01”,选择输出对应的载波f2;当yy值为“10”,选择输出3对应的载波f1;当yy值为“11”,选择输出对应的载波fo,即最终选择输出的载波波形就构成调制信号Y。当start为高电平时,进行调制,当输入的基带信号为1011 00 01 10 11 10 00 00 00,仿真结果如图2所示,选择相位分别为315°,45°,225°,135°,315°,45°,315°,225°,225°,225°。QPSK调制结构体的VHDL程序如下:

3 QPSK数字解调器仿真

3 QPSK数字解调器仿真

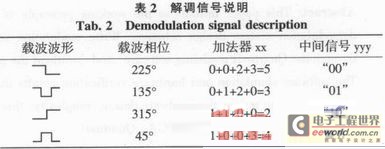

根据解调原理,MPSK解调电路的VHDL模型如图1所示,输入时钟信号clk及使能信号start,当start为高电平时才进行MPSK解调,输入已调信号x,设输入相位为225°,315°,45°,225°,135°,315°,45°,315°,225°,225°,225°,315°的载波波形,将一个信号周期分成4份,高电平权值分别为0,0、0、0.低电平权值分别1、1、2、3,如表2所示。

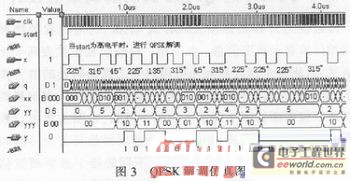

由图1可知,当调制信号x为低电平时,译码器1根据计数器q值。送入加法器XX相应的数据。经过反复的运算后,当q值为0和1时,加法器xx再将运算结果送到寄存器。译码器2根据yy数据通过译码,输出2位并行信号YYY。如表2所示,中间信号yy与YYY的关系为:5对应“00”;3对应“01”;2对应“10”,4对应“11”。并行信号YYY进行并/串转换后得到Y值。最终实现了相位为225°的载波,对应输出Y值为“00”相位为135°的载波,对应输出Y值为“01”;相位为315°的载波,对应输出Y值为“10”;相位为45°的载波,对应输出Y值为“11”。sta rt信号为高电平时开始解调信号,输出结果(y)为0010 11 00 01 10 11 10 00 00 00 10,仿真结果如图3所示。

4 结束语

本文基于VHDL方式实现了QPSK数字调制解调电路的设计,通过QuartusII软件建模对程序进行仿真,并通过引脚锁定,下载到FPGA芯片EP1K30TC144—3中,软件仿真和硬件验证结果表明了该设计的正确性和可行性,对比传统的电路设计有着明显的优点,简化设计,降低硬件电路的复杂性,并由于采用FPGA芯片,提高了设计的灵活性和可移植性,减小硬件设计的复杂性,便于移植维护和升级的特点。如为了防止相位模糊现象,采用差分编码,采用QDPSK调制解调系统,只需更改软件程序即可。

VHDLQPSK调制解调技 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)