基于ADF4110的频率发射系统

摘要:结合美国ADI公司推出低功耗宽带集成锁相环芯片ADF4110的性能特点以及锁相环频率合成器的原理,给出了用ADF4110锁相环芯片设计频率自动跟踪系统的硬件电路,并给出了频域和时域的测试结果,表明电路可以进行精确实时功率控制和本振频率控制,可以满足不同频点发射机的要求。

关键词:频率跟踪;锁相环;相位噪声;分频器

O 引言

利用锁相技术实现频率的加、减、乘、除。其优点是由于锁相环路相当于一窄带跟踪滤波器,因此能很好地选择所需频率的信号,抑制杂散分量,且避免了大量使用滤波器,十分有利于集成化和小型化。此外,一个设计良好的压控振荡器具有高的短期频率稳定性,而标准频率源具有高的长期频率稳定度,锁相式频率合成器把这二者结合在一起,使其合成信号的长期稳定度和短期稳定度都很高。但锁相式频率合成器的缺点是频率转换时间较长,单环频率合成器的频率间隔不可能做得很小。

1 锁相环结构

锁相环一般为一个负反馈环路结构,它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相,结构如图1所示。

鉴相器是用于判断锁相器所输出的时钟信号和接收信号中的时钟相差幅度。环路滤波器是用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与分频器的输出信号同频同相,即压控振荡器的输出信号频率为参考时钟频率的N倍。可调相/调频的时钟发生器是用于根据鉴相器所输出的信号来适当的调节锁相器,内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能。

锁相环有很多种类,可以是数字的也可以是模拟的也可以是混合的,可以用于恢复载波也可以用于恢复基带信号时钟。从整体上来说,输入与输出信号频率差不断减小,直到差值为零,进入锁定状态,相差等于一个极小的数值,实现频率跟踪。

2 ADF4110芯片介绍

ADF4110是分频为N的在无线接收器和发射机的上变频和下变频部分的一台小数N分频PLL频率合成器,它包括一台低噪声数字式阶段频率探测器(PFD),精确度极高的充电泵,并且有可编程序的参考分频器,一致的RF输出相位,工作电源2.7V到3.3V,串行接口,模拟式和数字式锁,电源下降沿工作方式,拥有环路滤波器。广泛应用于CATV设备,基础配置的无线收音机,无线手机,无线LANs和PMR,通信测试设备。ADF4110采用16脚下TSSOP封装,内部结构如图2所示。

CPGND充电泵地,此引脚是充电泵的接地回路。AVDD模拟电源电压,范围是3.0V~3.6V。对地的去耦电容应尽可能地靠近该引脚,AVDD必须与DVDD的值相同。AGND模拟信号地,此引脚是前置分频器和VCO的接地回路。RFINB,前置分频的互相输入,此引脚必须连接一个小旁路电容到地,用于去耦,典型值是l00PF。RFINA,前置分频器输入。该小信号输入是被交流耦合到VCO。RSET在此引脚和CPGND之间连接一个电阻,设置充电泵ICP最大输出电流。ICP和RSET的关系式为ICPmax=25.5/RSET,设置RSET=4.7KΩ,则ICPmax=5.42mA。DGND,数字地。REFIN,基准输入,此引脚是CMOS输入,输入能被TLL和CMOS晶体振荡器所驱动并能采用交流耦合。CLK串行时钟输入。

3 硬件系统电路

ADF4110内部的N分频器(包括P分频器、B分频器和A分频器三个部分)的分频比应为15000,即N=PB+A=15000。可选取P=64,B=237,A=32。

工作过程分为频率牵引过程和相位锁定过程,频率牵引过程是一个完全的非线性过程,相位锁定过程是一个近似的线性过程。电荷泵锁相环本质上是一个离散时间采样的动态系统,当环路带宽远远小于参考时钟频率时,可以采用连续时间近似;当相位误差在鉴频鉴相器的鉴相范围内时,可以采用线性近似,整个系统结构如图3所示,这样,当电荷泵锁相环处于相位锁定过程时,就可以得到一个线性连续时间的相位域模型。晶振输入的参考时钟频率为10MHz,压控振荡器的输出增益为,电荷泵电流为100mA,分频器的分频比N=16。根据电路参数,电荷泵锁相环的环路增益相对较高,为了保证电荷泵锁相环的稳定性,并抑制控制电压上的纹波,所以将此时钟倍频器中的三阶电荷泵锁相环设计成窄带锁相环,其开环单位增益带宽为fu=O.317MHz。同时,为了有相当的开环相位裕度和较快的闭环线性建立时间,取开环传输函数在单位增益带宽的相位裕度。最后得到C1=18.4nF,C2=88.9nF,C3=lO.0nF和R1=1.73kΩ,R2=160kΩ。

4 实验仿真结果

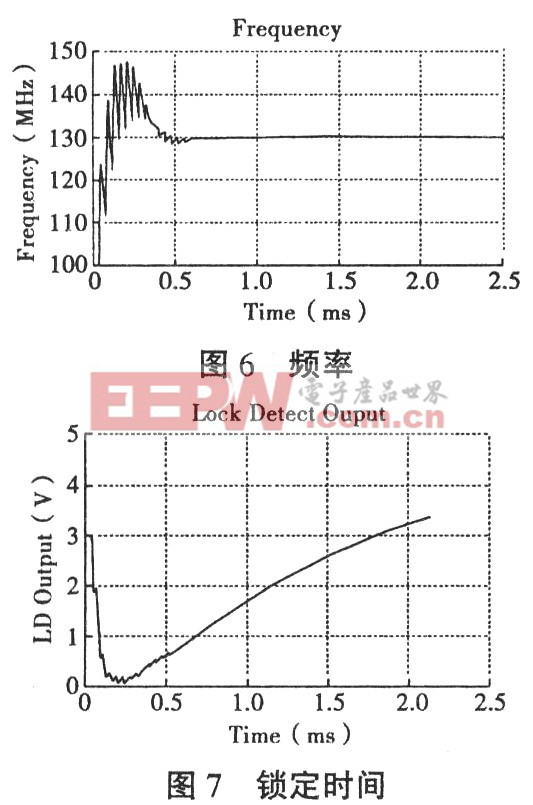

为了对所设计的系统分析其特性,本文在通用的仿真软件ADI SimPLL进行仿真。该软件本身提供有多种类型的环路滤波器,用户可根据需要选择滤波器,并输入所选定的VCO特性参数,这样,软件可自动计算出环路的各个参数以及相位噪声、锁定时间等。频域分析包括相位和环路增益,分别为图4和图5,消除了目前频率采用晶振取基准信号带来的各种不良影响;改进其输出频率的抖动特性;同时不存在直流放大器的零漂问题;不影响整体电路的性能,相位噪声平均≤一85dbc/Hz;谐波、杂散分布平均优于一65dbc。时域分析分析包括频率和锁定时间,分别为图6和图7。我们从图6和图7可以看出频率在114MHz是在锁定的,此时输出电压最小,解决了所定时间与相位抖动之间的矛盾,对信息的传输质量都有很大的提高。

- 第四代移动通信系统中的多天线技术(08-05)

- 透析信道效应对MIMO系统运作效能的影响(01-18)

- 如何发展中国第二代导航卫星系统(02-02)

- 北斗卫星导航系统的特点(02-02)

- 基于无线传送的智能家居室内通信系统(01-03)

- 基于WiMAX技术的5.8G无线专网射频系统设计(10-06)