基于FPGA的高速通信系统研究

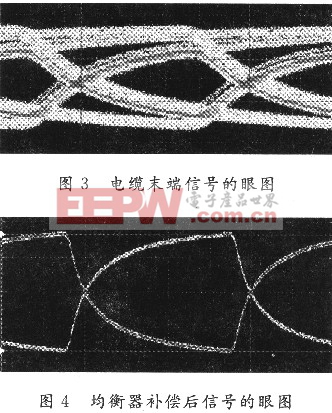

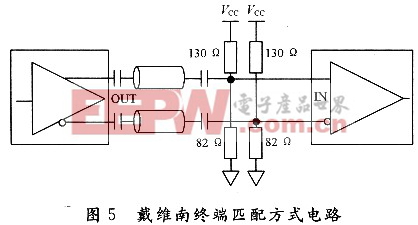

通过测试,此组传输器件可以驱动LVDS信号通过SVY-50-3型号电缆传输至少200 m。信号经过传输后,在电缆末端衰减严重,噪声和抖动也较严重。此时信号眼图如图3所示,可以看出信号质量差。直接接收此信号,会产生信号电平误判,而且信号的抖动将导致后级电路无法正常工作。接收均衡器CLC012自动为信号损耗提供补偿后,信号上的噪声和抖动均得到了改善,信号的眼图如图4所示。 LVDS驱动器由恒流源构成,因此需要做终端匹配。通常情况下在输入端并联100 Ω电阻从而满足互联系统要求的差分阻抗。在强噪声环境下,交流耦合连接时可以采用戴维南终端匹配方式提供1.2 V的偏置电压,同时满足100 Ω差分阻抗的设计要求。具体方法是将LVDS的+/-端通过130 Ω电阻上拉至VCC,同时下拉82 Ω电阻到地,如图5所示,电阻精度要求在1%。

2.3 电路PCB设计

在PCB设计过程中,要注意电路板的布局。模拟电路和数字电路需要分开,使用单点接地的方式相连。将边沿速率变化快的VTTL/LVCMOS信号与LVDS信号布在不同信号层上,并用电源和底层隔开,减小耦合到LVDS线路上的串扰。LVDS走线要遵循以下规则:

(1)差分对两根信号从芯片扇出后就尽量靠近(紧耦合),这样有助于消除反射,确保耦合的噪声是共模形式。

(2)对内信号的布线长度要保持一致,以减小信号延时,长度匹配控制在10 mil以内。

(3)对内信号保持固定的线间距,避免因为线间距变化导致差分阻抗不连续。

(4)差分对间尽量远离,减少线间串扰,必要时在差分对间放置隔离用的接地过孔。

(5)尽量减少差分信号线上过孔的个数,避免走90°拐角,使用圆弧或者45°折线代替。

(6)LVDS信号不能跨平面分割,否则会因为缺少参考平面而导致阻抗不连续,要给LVDS信号设置完整的参考平面。

(7)匹配电阻尽可能靠近接收端。

3 系统的逻辑设计

3.1 时钟部分设计

时钟信号由电路板上40 MHz晶振提供。通过数字时钟管理单元DCM钟倍频得到120 MHz的系统的工作时钟。使用DCM模块时,注意DCM的输入和输出需要通过BUFG单元与全局时钟资源相连。全局时钟资源使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,使全局时钟到达芯片内部所有逻辑单元的时延和抖动都为最小。DCM在时钟锁定后使能LOCK信号,表示时钟倍频工作完成,使用这个信号作为FPGA内部其他逻辑的复位。

3.2 异步时钟域变换

系统输入信号工作在不同的异步时钟域,需要在FPGA内部将信号变换到同一个时钟域。

串口信号速度低,可以使用系统时钟高速采集的方式。根据奈奎斯特抽样定律,抽样频率大于2倍信号最高频率,就可以从抽样信号中无失真地恢复原信号。本系统使用高于5倍串口波特率的时钟去采集串口数据。经过误码仪的大量测试,串口数据能够被正确接收和恢复。

视频信号是并行信号,采用高速采集的方法会增加数据量,不适合本系统。本系统采用双口FIFO完成异步时钟域转换。S3C500E片内的Block RAM资源可以灵活的生成双口FIFO,与普通逻辑单元生成的双口FIFO相比,它的稳定性高,最高读写速度快,产生亚稳定状态的概率小。双口FIFO的输入端连接系统输入信号的时钟和数据;在输出端连接系统时钟数据。双口FIFO的读取时钟速度必须高于写入速度,以避免FIFO存满后溢出导致有效数据丢失。另一方面,慢时钟域向快时钟域转换的时候,FIFO会出现读取空的状态,此时将取出无效数据(这些数据是FIFO中最后一个数据的重复)。无效数据通过串行数据帧传输到接收端,会导致恢复后输出信号出现误码。所以系统将FIFO的空标志empty信号添加到数据帧,用于识别无效数据。

3.3 数据组帧及编码

同步传输需要将原始数据组成数据帧再进行发送,即在数据间添加起始位、停止位和校验位。数据帧的起始位过长会影响传输效率,过短会增加接收端识别的难度。本系统选用80 b为一帧,起始位为8 b,停止位为2 b,奇校验位为1 b。接收端逻辑通过对多个数据帧分析后,定位数据帧的起始位。由于每帧数据长度固定,所以找到某一帧的起始位后可以周期性的计算出接下来各帧的起始位置,不再需要反复做识别工作。

数据组帧后信号的平均位速率可能低于CLC012的最低工作频率,不能直接用于传输,还需要对其进行8B/10B编码。8B/10B技术是将8个数据位经过某种映射的机制转化为10个数据位的字码,可使发送的“O”、“1”数量保持一致,连续的“1”或“0”基本不超过5位。8 B/10 B编码技术保证了传输的DC平衡,增加了信息传输的可靠性。系统使用Xilinx公司提供的8 B/10 B编码和解码IP核,减少了系统的开发周期,增加了系统的稳定性。8 B/10 B编码及解码IP的模块原理图如图6和图7所示。

收发器 相关文章:

- W-CDMA收发器的功率管理技术(08-01)

- 射频捷变收发器AD9361(03-07)

- 射频收发器在航空航天和防务中的应用(10-25)

- MAX2550-MAX2553收发器Femtocell无线参考设计(08-18)

- Atheros对Ralink,看WiFi产品的射频电路设计(10-05)

- 设计新突破,可降低90%的DPD功耗芯片出炉(07-18)