空分复用MIMO通信系统简介及FPGA实现

阵可用的处理时间。对选中的 FPGA 而言,其目标时钟频率为 225MHz,通信带宽为 5MHz(相当于 WiMAX 系统中的 360 个数据子载波),每个信道矩阵间隔可用的处理时钟周期数为 64。

我们采用硬件功能单元精湛的流水线和时分复用 (TDM) 功能,以达到 WiMAX OFDM 符号的实时要求。

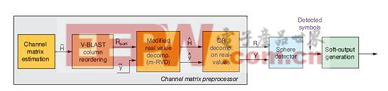

除了高数据率外,在架构设计指导过程中控制子模块时延也是一个重要的问题。我们通过引入连续信道矩阵的 TDM 解决了时延问题。这种方法可以延长同一信道矩阵元之间的处理时间,同时还能保持较高的数据吞吐量。构成 TDM 组的信道数会随着子模块的不同而变化。在 TDM 方案中,信道矩阵求逆过程用了 5 个信道,而有 15 个信道在实数 QR 分解模块中进行了时分复用。图 2 是该系统的高级流程图。

图 2. MIMO 802.16e 宽带无线接收器的高级流程图信道矩阵预处理

信道矩阵预处理器确定了空分复用复合信号每一层的最佳检测次序。该预处理器负责计算信道矩阵的伪逆矩阵范数,并根据这些范数,选择待处理的下一个传输流。伪逆矩阵中范数最小的行对应着最强传输流(检波后噪声放大最小),而范数最大的行对应着质量最差的层(检波后噪声放大最大)。我们的实施方案首先检测最弱的层,然后按最低噪声放大到最高噪声放大的次序逐层检测。对排序过程中的每一步,信道矩阵中相应的列随后会被清空,然后简化后的矩阵进入下一级的天线排序处理流水线。

在预处理算法中,伪逆矩阵的计算要求最高。这个过程的核心是矩阵求逆,通常通过吉文斯(Givens) 旋转进行 QR 分解 (QRD) 来实现。常用的角度估算和平面旋转算法(如 CORDIC)会造成严重的系统时延,对我们的系统来说是不可接受的。因此,我们的目标是运用 FPGA 的嵌入式 DSP 资源(比如 Virtex-5 器件中的 DSP48E),找出矢量旋转和相位估算的替代性解决方案。

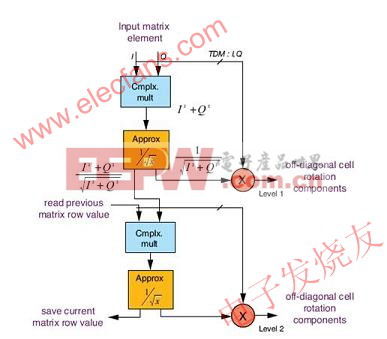

QRD 的脉动阵列结构由两种类型的处理单元构成——对角线单元或边界单元和非对角线单元或内部单元。边界单元执行矢量函数,可以生成阵列内部单元使用的旋转角度。要想得到想要的旋转角度,可以把非对角线单元中的值与对角线单元中的共轭复数相乘,然后除以复数的倒数即可。相除实际是用乘法的方式完成的,即在观察到函数接近线性的时候,乘以根据定义的间隔的多项式近似值计算出的倒数。图 3 显示了采用这种近似值在对角线脉动单元中完成这种复杂旋转的信号流程图。

图 3. 对角线脉动单元结构图

发送到非对角线单元中的数据是旋转矢量的同相部分和正交部分除以相应的近似值得出的结果。我们不仅通过在对角线单元和非对角线单元采用流水线架构实现了高数据吞吐量,同时还通过对跨5个信道的硬件进行时分复用的方式控制了近似值模块和复杂乘法器引起的时延。

对 4x4 矩阵,我们使用了 1 个对角线单元和 7 个非对角线单元。分解单个矩阵所花的处理时间为 4x4=16 个数据周期,而该设计交付数据的速度是每三个时钟周期一个样本,因此分解单个矩阵的所用的总时长为 3x4x4=48 个时钟周期(低于可用的 64 个时钟周期)。我们对分解后的矩阵使用了回代法(back subsTItution),同时以相同的 TDM 方式进一步进行了重新排序操作。

球形检测器

球形检测器采用PED 单元进行范数计算。根据树的层次,我们采用了三种不同类型的 PED 单元。根节点 PED 模块负责计算所有可能的 PED。二级 PED 模块针对上一级计算得出的 8 个幸存路径计算出 8 个可能的 PED。这样在树的下一级索引中,我们就有 64 个生成的 PED。第三种类型的PED模块用于其它树级,负责计算上一级计算出的所有 PED 的最邻近的节点 PED。

球形检测器 (SD) 的流水线架构可以在每个时钟周期中处理数据。其结果就是树的每级只需要一个 PED 模块。因此,对 4x4 64-QAM 系统而言,PED 单元的总数为 8,与树的级数相等。

SD 可以采用硬解码和软解码两种类型的解码技术。硬解码能够用贯穿树的各级的最小距离矩阵度量次序;软解码,用对数似然比来代表输出的每个比特。对数似然比一般被当作优先输入值提供给信道解码器,比如 turbo 解码器。

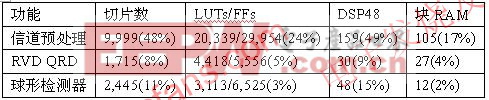

FPGA资源占用

实施和仿真包括图 2 所示的检测过程,但不包括软输出生成模块。目标芯片是 Virtex-5 XC5VFX130T-2FF1738 FPGA。设计的时钟频率为 225MHz,可用的数据率为 83.965Mb/s。

表 1 显示了设计中每个主要功能单元的资源占用情况。利用率 (%) 表示 FPGA 面积占XC5VFX130T 器件总面积的百分比。

表 1. 按子系统划分的资源占用情况

System Generator 和基于模型的设计

我们使用针对 DSP 设计流程的赛灵思 System Generator 实现了完整的硬判链

简介 FPGA 实现 系统 通信 复用 MIMO 空分 相关文章:

- CCBN简介(03-19)

- 新型谐振式螺旋天线的设计原理简介(11-04)

- 高频链技术简介(11-04)

- 基于nRF401的通用智能无线收发装置简介(10-07)

- 馈线与天线的连接方法简介(10-07)

- 无线自组网技术VBee简介及其应用实例(10-07)