使用高速SRAM设计电池支持型存储器

时间:03-04

来源:互联网

点击:

嵌入式系统的性能取决于其软硬件能力。一个编写合理的软件可以利用硬件的所有能力发挥后者的最大性能。与此类似,无论软件设计多么合理,低效的硬件都可能影响系统性能。

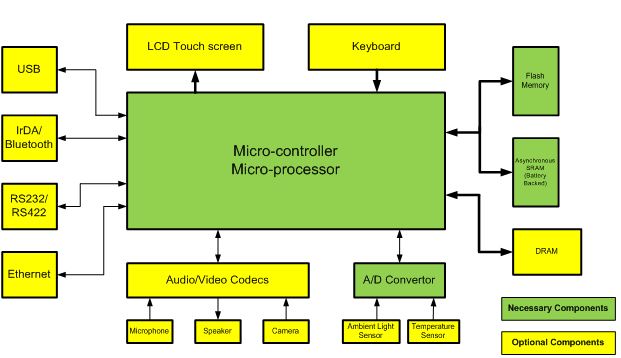

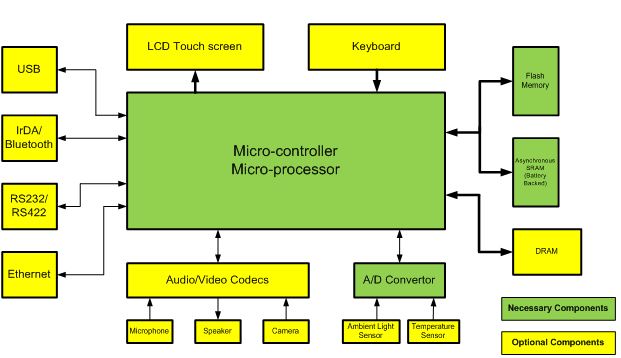

数十年来,传统嵌入式系统的结构一直没有改变。图1显示了一个典型嵌入式系统的框图。一个微控制器和一个微处理器位于系统的核心。按照具体应用,系统设计人员可根据需要删减接口和外设。如果控制器的内置存储器不足,就需要使用闪存、SRAM、DRAM等外置存储器。通常而言,闪存用于存储控制器执行的代码,而SRAM用于存储运行时临时变量和保存重要的应用数据块。

图1:一个典型嵌入式系统的框图

功耗预算和性能一直是选择系统组件-无论是控制器还是外设-的两大标准。如果性能是最为重要的标准,则设计人员倾向于选择速度最快的组件,从而弥补较高的功耗预算。同样,如果功耗是最重要的标准(例如,对于电池供电型系统而言),则设计人员倾向于选择功耗最低的组件。因此,嵌入式系统通常分为三类:

1.永远“处于开机状态”的系统:此类系统可保证它们能够从一个不间断电源获得电能。这些系统是高性能系统,可以最高的运行频率工作。

2.电池供电型系统:一块板载电池是此类系统的唯一电源(如手机)。虽然性能是此类系统的一个重要标准,但更长的电池续航时间最为重要。因此,这些系统使用功耗最低的组件。

3.电池支持性系统:此类系统必需能够可靠地运行,即使在失去板载电源的情况下也是如此。为了在断电时避免丢失重要数据,系统设计人员会提供一块小电池(通常是一颗240mAh的纽扣电池),以便为SRAM保留等功能提供备用电源,并维持实时时钟(RTC)。

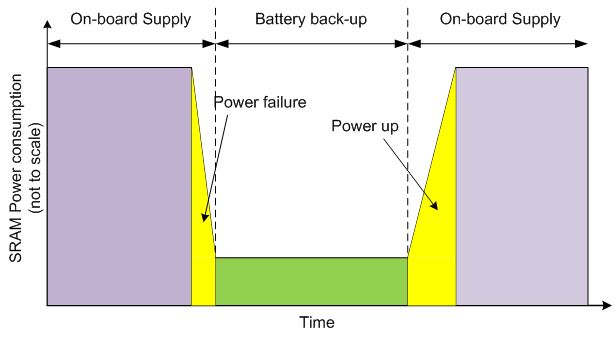

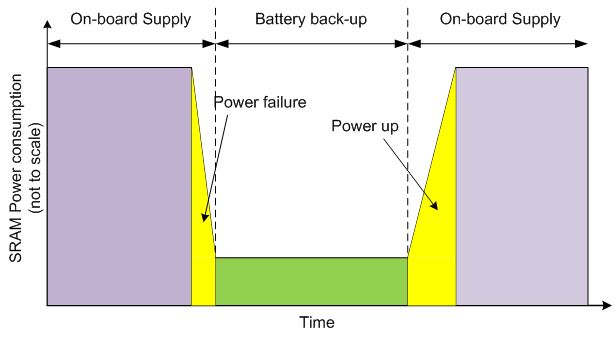

正常运行时,电池支持型系统使用可用电源工作。根据存储器映射,它可以从闪存提取代码,然后将结果存储到SRAM中。即使是在断电时,存储这些数据变得也很重要。为了解决这个问题,SRAM被连接到一块备用板载电池。正常运行时,板载电源负责为系统供电;断电时,一块监控芯片将把SRAM的电源切换到板载电池,并将SRAM置于待机模式。图2显示了电池支持型系统中SRAM的典型功耗。正常运行时,监控芯片使用板载电源。断电时,SRAM被监控芯片切换到板载电池,并被禁用。只要电池有电,系统可以一直处于这一模式。一旦板载电源恢复,监控芯片将逐渐使用板载电源为SRAM供电。通常而言,此类芯片需要1ms-10ms完成这个过渡。这段时间系统不会受到影响,这是因为控制器也需要同样长的时间完成其上电复位程序。

图2:电池支持型系统的功耗模式

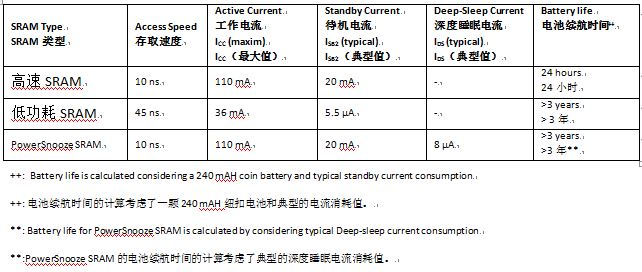

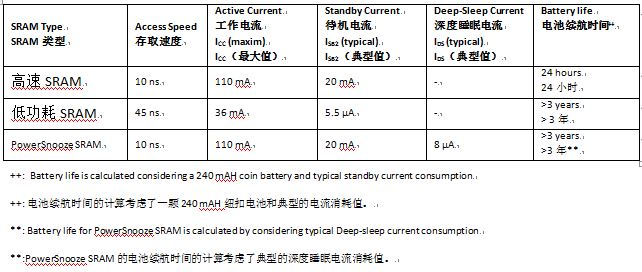

当此类系统部署到现场时,维修它们会很不方便。事实上,这些系统两三年内不用维修。因此,电池续航时间变得非常重要。系统设计人员倾向于选用那些在待机模式下消耗电流最少的SRAM。如果观察一下市场上出售的SRAM(见表1),你会发现设计人员在选择SRAM时没有太多选择。对更长的电池续航时间的需求让他们几乎不可能选择一个高速SRAM。搭载一颗240mAH纽扣电池的一个16Mb高速SRAM仅能提供12小时的续航时间,而一个低功耗SRAM却能提供长达三年的电池续航时间。

表1:SRAM16Mb SRAM产品组合

所有系统的性能都遵从阿姆达尔定律。简而言之,阿姆达尔定律规定:一个系统的速度是其最慢组件的速度。过去几十年,微控制器厂商推出了能够以高于150 MHz的速度运行的控制器。很多此类控制器内置低功耗和/或深度睡眠模式,当系统需要由电池供电时,它们能够实现较快的运行速度和较低的功耗。

但是,如果外设组件不能匹配其速度,一个较快的控制器将无法提升性能。外置内存接口是一个重要的高速链路,而一个低性能的闪存或SRAM可能会成为瓶颈。闪存的初始访问时间为60-80ns。但随着Page、Burst、eXecute In Place (XIP)等各类模式的出现,闪存芯片的读速度提高了三倍,从而让控制器能够在20-30 ns 内(即150 MHz控制器的2到3个时钟周期)从闪存读取数据。但是,选择低功耗SRAM意味着控制器仍然需要45 -70ns的时间来访问SRAM(4到10个时钟周期)。

为了了解这种性能选择的效应,我们可以设想有一个系统,它在1ms内循环执行一段代码,其中微控制执行代码的时间占70%,将结果(关键变量)存储到SRAM中的时间占剩余的30%。使用一个较快的处理器应能确保大幅缩短这一执行时间。凭借其改良运行模式,闪存能够匹配这个速度,并将代码执行时间缩短三分之二(从700到230us)。但是,选择一个低功耗SRAM,意味着SRAM存取速度没有提升。理想的情况是,这个系统的执行时间应缩短300%(从1ms到330us),但由于使用了低功耗SRAM,执行时间仅缩短了200%(从1ms到550us)。

对速度的需求

你开车时车速越快,油耗就越高。这个简单的原则同样适用于嵌入式系统,此时SRAM是车,电池续航时间则是里程数。在上述场景中,系统设计人员既可以选择一个高速SRAM(存取时间为10ns)来提升系统性能,但牺牲电池续航时间,也可以选择一个低功耗SRAM,但牺牲系统性能。

存储器厂商发现市场需要兼具快速和低功耗的SRAM。除了常见的运行模式―工作和待机―之外,这些SRAM还有一个名为“深度睡眠”的低功耗模式。深度睡眠模式由一个输入信号控制,该信号可在断言后将设备置于深度睡眠模式。例如,与低功耗SRAM的45-55ns的存取速度相比,赛普拉斯的PowerSnooze(电力打盹)SRAM提供10ns的存取速度。在功耗方面,其深度睡眠电流在10-20uA范围内,而一个16M高速SRAM的待机电流则高达 30 - 40mA。表2对比了三类SRAM的速度、电流消耗等关键参数。

表2:三种类型的SRAM对比

系统设计人员可以通过一个GPIO 控制深度睡眠模式的进入,或者使用监控芯片自动控制模式切换。对于GPIO控制,软件可以通过分析SRAM存取利用其深度睡眠模式。

电池支持型低功耗SRAM

对于电池支持型存储器额外电路的需求源于以下事实:断电时,控制器将丧失其I/O驱动功能。这会导致信号线路上出现中间逻辑电平,后者将通过板载电容和泄漏逐渐向低电压处放电。失去控制意味着即使SRAM开始由电池供电,芯片启用信号 (ˉCE)将变为逻辑低状态,从而启用SRAM。为了避免这个问题,系统设计人员使用一块监控芯片监测板载电源,并控制SRAM芯片启用信号。

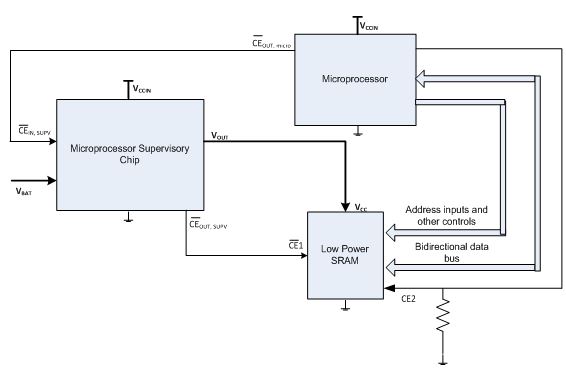

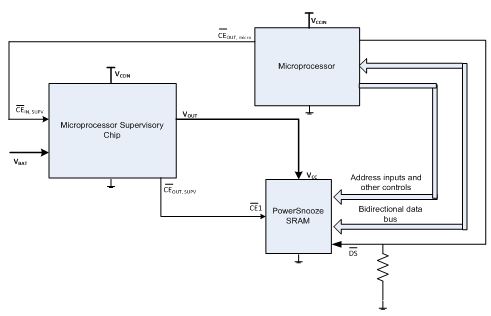

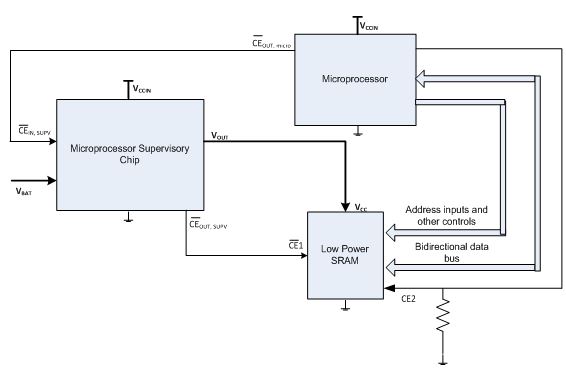

图3详细描述了SRAM、处理器接口和监控芯片。所有地址和数据线以及控制信号均由处理器驱动。SRAM的主用低电平芯片启用信号由监控芯片驱动,后者由来自控制器的芯片启用信号驱动。正常运行时(即板载电源可用时),监控芯片对于控制器和SRAM完全透明,但在断电时,监控芯片将接管对去往SRAM的芯片启用信号的控制,将其变为逻辑高状态,同时忽略控制器的芯片启用信号。这个监控芯片将板载电源无缝切换至电池,并禁用SRAM,从而避免数据丢失。第二个芯片启用信号是高电平有效信号,由控制器通过一个弱下拉直接驱动。这个弱下拉可确保断电时第二个芯片启用信号被下拉到逻辑低状态,并禁用SRAM。

图3:电池支持型低功耗SRAM

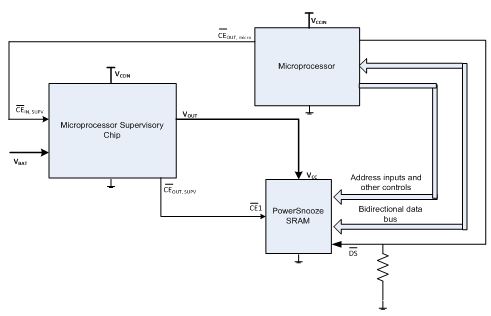

对于那些在断电时使用备用电池的应用,高速、低功耗SRAM较低的深度睡眠电流使其成为这些应用的理想选择。正常运行时,SRAM可以高速运行,而断电时,SRAM可以通过将深度睡眠信号断言到逻辑低状态而自动切换到深度睡眠模式。图4显示了在不改变一个低功耗SRAM的现有设计的情况下,如何使用一个带深度睡眠模式的SRAM。

断电时,监控芯片禁用SRAM,而深度睡眠引脚上的下拉将自动把信号下拉到逻辑低状态,从而允许该部分进入深度睡眠模式。监控芯片确保板载电源不可用时SRAM一直处于禁用状态。电源恢复后,监控芯片将继续保持SRAM的禁用状态,直到其上电复位超时。这个超时时段从1到100ms不等,具体取决于所选择的监控芯片。超时时段允许控制器成功启动,之后它可以控制深度睡眠信号,并将其转变为逻辑高状态。这能够管理高速、低功耗SRAM的深度睡眠退出时序,同时使之用于控制器访问。

图4:带有高速、低功耗SRAM的备用电池

高速、低功耗SRAM可提供相当于传统低功耗SRAM的电池备用时间,同时通过提高SRAM的访问速度满足系统设计人员的性能提升要求。

数十年来,传统嵌入式系统的结构一直没有改变。图1显示了一个典型嵌入式系统的框图。一个微控制器和一个微处理器位于系统的核心。按照具体应用,系统设计人员可根据需要删减接口和外设。如果控制器的内置存储器不足,就需要使用闪存、SRAM、DRAM等外置存储器。通常而言,闪存用于存储控制器执行的代码,而SRAM用于存储运行时临时变量和保存重要的应用数据块。

图1:一个典型嵌入式系统的框图

功耗预算和性能一直是选择系统组件-无论是控制器还是外设-的两大标准。如果性能是最为重要的标准,则设计人员倾向于选择速度最快的组件,从而弥补较高的功耗预算。同样,如果功耗是最重要的标准(例如,对于电池供电型系统而言),则设计人员倾向于选择功耗最低的组件。因此,嵌入式系统通常分为三类:

1.永远“处于开机状态”的系统:此类系统可保证它们能够从一个不间断电源获得电能。这些系统是高性能系统,可以最高的运行频率工作。

2.电池供电型系统:一块板载电池是此类系统的唯一电源(如手机)。虽然性能是此类系统的一个重要标准,但更长的电池续航时间最为重要。因此,这些系统使用功耗最低的组件。

3.电池支持性系统:此类系统必需能够可靠地运行,即使在失去板载电源的情况下也是如此。为了在断电时避免丢失重要数据,系统设计人员会提供一块小电池(通常是一颗240mAh的纽扣电池),以便为SRAM保留等功能提供备用电源,并维持实时时钟(RTC)。

正常运行时,电池支持型系统使用可用电源工作。根据存储器映射,它可以从闪存提取代码,然后将结果存储到SRAM中。即使是在断电时,存储这些数据变得也很重要。为了解决这个问题,SRAM被连接到一块备用板载电池。正常运行时,板载电源负责为系统供电;断电时,一块监控芯片将把SRAM的电源切换到板载电池,并将SRAM置于待机模式。图2显示了电池支持型系统中SRAM的典型功耗。正常运行时,监控芯片使用板载电源。断电时,SRAM被监控芯片切换到板载电池,并被禁用。只要电池有电,系统可以一直处于这一模式。一旦板载电源恢复,监控芯片将逐渐使用板载电源为SRAM供电。通常而言,此类芯片需要1ms-10ms完成这个过渡。这段时间系统不会受到影响,这是因为控制器也需要同样长的时间完成其上电复位程序。

图2:电池支持型系统的功耗模式

当此类系统部署到现场时,维修它们会很不方便。事实上,这些系统两三年内不用维修。因此,电池续航时间变得非常重要。系统设计人员倾向于选用那些在待机模式下消耗电流最少的SRAM。如果观察一下市场上出售的SRAM(见表1),你会发现设计人员在选择SRAM时没有太多选择。对更长的电池续航时间的需求让他们几乎不可能选择一个高速SRAM。搭载一颗240mAH纽扣电池的一个16Mb高速SRAM仅能提供12小时的续航时间,而一个低功耗SRAM却能提供长达三年的电池续航时间。

表1:SRAM16Mb SRAM产品组合

所有系统的性能都遵从阿姆达尔定律。简而言之,阿姆达尔定律规定:一个系统的速度是其最慢组件的速度。过去几十年,微控制器厂商推出了能够以高于150 MHz的速度运行的控制器。很多此类控制器内置低功耗和/或深度睡眠模式,当系统需要由电池供电时,它们能够实现较快的运行速度和较低的功耗。

但是,如果外设组件不能匹配其速度,一个较快的控制器将无法提升性能。外置内存接口是一个重要的高速链路,而一个低性能的闪存或SRAM可能会成为瓶颈。闪存的初始访问时间为60-80ns。但随着Page、Burst、eXecute In Place (XIP)等各类模式的出现,闪存芯片的读速度提高了三倍,从而让控制器能够在20-30 ns 内(即150 MHz控制器的2到3个时钟周期)从闪存读取数据。但是,选择低功耗SRAM意味着控制器仍然需要45 -70ns的时间来访问SRAM(4到10个时钟周期)。

为了了解这种性能选择的效应,我们可以设想有一个系统,它在1ms内循环执行一段代码,其中微控制执行代码的时间占70%,将结果(关键变量)存储到SRAM中的时间占剩余的30%。使用一个较快的处理器应能确保大幅缩短这一执行时间。凭借其改良运行模式,闪存能够匹配这个速度,并将代码执行时间缩短三分之二(从700到230us)。但是,选择一个低功耗SRAM,意味着SRAM存取速度没有提升。理想的情况是,这个系统的执行时间应缩短300%(从1ms到330us),但由于使用了低功耗SRAM,执行时间仅缩短了200%(从1ms到550us)。

对速度的需求

你开车时车速越快,油耗就越高。这个简单的原则同样适用于嵌入式系统,此时SRAM是车,电池续航时间则是里程数。在上述场景中,系统设计人员既可以选择一个高速SRAM(存取时间为10ns)来提升系统性能,但牺牲电池续航时间,也可以选择一个低功耗SRAM,但牺牲系统性能。

存储器厂商发现市场需要兼具快速和低功耗的SRAM。除了常见的运行模式―工作和待机―之外,这些SRAM还有一个名为“深度睡眠”的低功耗模式。深度睡眠模式由一个输入信号控制,该信号可在断言后将设备置于深度睡眠模式。例如,与低功耗SRAM的45-55ns的存取速度相比,赛普拉斯的PowerSnooze(电力打盹)SRAM提供10ns的存取速度。在功耗方面,其深度睡眠电流在10-20uA范围内,而一个16M高速SRAM的待机电流则高达 30 - 40mA。表2对比了三类SRAM的速度、电流消耗等关键参数。

表2:三种类型的SRAM对比

系统设计人员可以通过一个GPIO 控制深度睡眠模式的进入,或者使用监控芯片自动控制模式切换。对于GPIO控制,软件可以通过分析SRAM存取利用其深度睡眠模式。

电池支持型低功耗SRAM

对于电池支持型存储器额外电路的需求源于以下事实:断电时,控制器将丧失其I/O驱动功能。这会导致信号线路上出现中间逻辑电平,后者将通过板载电容和泄漏逐渐向低电压处放电。失去控制意味着即使SRAM开始由电池供电,芯片启用信号 (ˉCE)将变为逻辑低状态,从而启用SRAM。为了避免这个问题,系统设计人员使用一块监控芯片监测板载电源,并控制SRAM芯片启用信号。

图3详细描述了SRAM、处理器接口和监控芯片。所有地址和数据线以及控制信号均由处理器驱动。SRAM的主用低电平芯片启用信号由监控芯片驱动,后者由来自控制器的芯片启用信号驱动。正常运行时(即板载电源可用时),监控芯片对于控制器和SRAM完全透明,但在断电时,监控芯片将接管对去往SRAM的芯片启用信号的控制,将其变为逻辑高状态,同时忽略控制器的芯片启用信号。这个监控芯片将板载电源无缝切换至电池,并禁用SRAM,从而避免数据丢失。第二个芯片启用信号是高电平有效信号,由控制器通过一个弱下拉直接驱动。这个弱下拉可确保断电时第二个芯片启用信号被下拉到逻辑低状态,并禁用SRAM。

图3:电池支持型低功耗SRAM

对于那些在断电时使用备用电池的应用,高速、低功耗SRAM较低的深度睡眠电流使其成为这些应用的理想选择。正常运行时,SRAM可以高速运行,而断电时,SRAM可以通过将深度睡眠信号断言到逻辑低状态而自动切换到深度睡眠模式。图4显示了在不改变一个低功耗SRAM的现有设计的情况下,如何使用一个带深度睡眠模式的SRAM。

断电时,监控芯片禁用SRAM,而深度睡眠引脚上的下拉将自动把信号下拉到逻辑低状态,从而允许该部分进入深度睡眠模式。监控芯片确保板载电源不可用时SRAM一直处于禁用状态。电源恢复后,监控芯片将继续保持SRAM的禁用状态,直到其上电复位超时。这个超时时段从1到100ms不等,具体取决于所选择的监控芯片。超时时段允许控制器成功启动,之后它可以控制深度睡眠信号,并将其转变为逻辑高状态。这能够管理高速、低功耗SRAM的深度睡眠退出时序,同时使之用于控制器访问。

图4:带有高速、低功耗SRAM的备用电池

高速、低功耗SRAM可提供相当于传统低功耗SRAM的电池备用时间,同时通过提高SRAM的访问速度满足系统设计人员的性能提升要求。

- 低功耗嵌入式实现的方方面面(04-30)

- 功率与控制的结合使LED照明方案灵活、简便(10-20)

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 几种实用的低电压冗余电源方案设计(01-26)

- 基于先验预知的动态电源管理技术(03-28)

- 基于CAN通信的电源监控系统的设计(04-06)