设计超低功耗的嵌入式应用:五种电源模式详解

时间:11-17

来源:互联网

点击:

通常说来,SoC相对于传统MCU而言能支持更多低功耗模式。其原因在于SoC集成度高,有更多片上组件和多种电源配置,以支持不同的工作需求。电源模式的数量与每种模式下的可用资源根据器件会有所不同。举例来说,在某种低功耗模式下,某个器件能在仅保持寄存器和RAM内容的情况下给所有其它组件断电,而另一种器件则只是给CPU断电,而让其它资源继续运行。不同制造商会对这些模式采取不同的命名方法。在本文中,我们将以赛普拉斯的PSoC 4器件为例来详细介绍各种电源模式。

以下电源模式也得到其它制造商的大多数设备的支持:

●工作模式

●休眠模式

●深度休眠模式

●冬眠模式

●停止模式

下面我们来看看这些电源模式的具体情况:

1.工作模式:在此模式下,CPU和所有片上其它资源都正常工作运行。该模式是系统整体功耗的最主要组成部分。在此模式下,如果不使用的话,可将芯片上的各种外设分别断电。

2.休眠:这是控制器另一种常见的电源模式。该模式主要与CPU有关。当CPU进入休眠状态后,其时钟移除。CPU这时对总功耗的唯一影响就是静态功耗,因为这时已经没有时钟开关切换工作,也就不会有动态功耗。ADC和比较器等其它外设在此模式下可用。

3. 深度休眠:此电源模式下即便是系统时钟也被禁用,所以在此模式下所有高频资源都不可用。不过,这些资源的当前状态不受影响,也就是说CPU寄存器、 SRAM等的当前状态不受影响。由于高频时钟被禁用,因此能节约开关消耗的功率。通常情况下,深度休眠模式提供低频时钟运行的选项,低频时钟可用来驱动定时器等低频资源。此外,该模式也允许开发人员使用I2C从设备等通信协议块,其无需器件自身生成时钟。由于进入此模式的主要方法就是禁用系统主时钟,因此这是可以实现的。然而,模块仍然可通电。该模式对功耗的影响主要在于片上所有时钟的静态功耗。

4.冬眠:在此模式下,所有时钟都关闭,包括低速振荡器。片上所有资源,除了用于外部事件触发唤醒的资源以外全都断电。由于本模式下几乎所有组件都断电,因此该模式能减少静态和动态功耗组件,从而实现最低功耗。

5.停止:顾名思义,停止模式就是所有外设断电,即使是RAM和CPU寄存器的内容也不保持。在PSoC 4等类似器件中,这种模式下仅保持IO引脚的状态。从这种模式下唤醒会进入芯片重启动。

当分析一款应用的功耗时,必须查看所有电源模式下的功耗情况。

必须明确某种模式下能提供唤醒源。举例来说,需要某种中断才能从休眠模式唤醒,在冬眠模式下则需要I2C地址匹配中断以唤醒器件。需要了解每种模式下有哪些资源工作,能提供什么唤醒资源。举例来说,系统中可用比较器中断作为唤醒源,在超出设定阈值情况下可用模拟输入唤醒系统。就图1所示的应用而言,唤醒需要采用GPIO中断或者甚至硬复位,因为RTC会随时运行,而且控制器不需要保持此前的状态。

冬眠和停止模式下,功耗可低至100nA。对于RTC本身而言,您会很容易找到功耗很低的RTC(仅消耗100-200nA)。假设控制器直接驱动LCD,我们可认为LCD的关闭状态功耗为零。

这就使得图1所示系统中的平均功耗在300nA的范围内。如果我们假设设计方案采用CR2032作为电源,电池容量约为225mAh。就300nA的电流来说,电池仅在器件始终处于断电模式下能支持70到80年的工作。

每次按下按键,控制器都会唤醒。这会将控制器的功耗提升到500μA-1mA的范围。假设功耗为1mA左右,控制器从RTC获取数据并显示在LCD 上。控制器执行这项工作只需很短的时间,但显示屏要保持较长工作时间(假设说显示屏亮起10秒钟确保用户看到数据)。作为直接驱动LCD,控制器必须保持较长的工作时间,也就是要消耗更多电荷。在此情况下,赛普拉斯的PSoC4等器件可提供低功耗模式,能让设备关闭所有其它外设,仅运行驱动LCD所需的模块。在这种器件中,LCD驱动运行在特定的低功耗模式下,这种模式被称为数字关联模式。其结果就是大幅减少电流消耗。

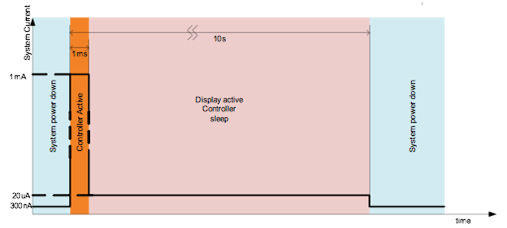

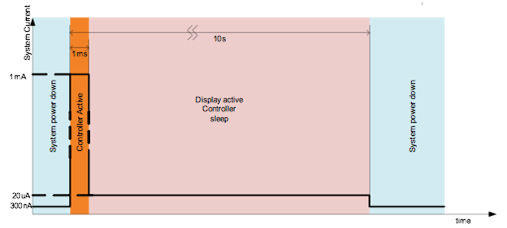

图2:各种状态下的电流消耗

每次按键都会经历如图2所示的电流曲线。曲线下方区域是单次按键的典型功耗。消耗的电荷计算如下:

Q = (1mA*1ms) + (20μA*10s)

根据上面的数据,我们可计算出给定电源能支持多少次按键。

工作模式下所花的时长非常重要,因为这种模式下耗电最大。一个选项是让MCU保持工作模式,但CPU时钟速度较低,从而降低工作模式下的耗电。不过,这会导致更高的平均功耗,因为工作模式所花的时间取决于时钟频率。此时由于MCU必须处于工作模式,因此功耗取决于MCU处理数据所花的时间。更快速的 MCU能很快完成任务,从而延长处于低功耗模式下的时间,也就能让系统减少功耗。系统设计人员可根据系统要求明确最佳配置。

在本系列文章的下一部分,我们将以更大型系统为例作讲解,并介绍如何降低平均功耗。此外,我们还将探讨一些降低平均功耗的系统级技巧。

以下电源模式也得到其它制造商的大多数设备的支持:

●工作模式

●休眠模式

●深度休眠模式

●冬眠模式

●停止模式

下面我们来看看这些电源模式的具体情况:

1.工作模式:在此模式下,CPU和所有片上其它资源都正常工作运行。该模式是系统整体功耗的最主要组成部分。在此模式下,如果不使用的话,可将芯片上的各种外设分别断电。

2.休眠:这是控制器另一种常见的电源模式。该模式主要与CPU有关。当CPU进入休眠状态后,其时钟移除。CPU这时对总功耗的唯一影响就是静态功耗,因为这时已经没有时钟开关切换工作,也就不会有动态功耗。ADC和比较器等其它外设在此模式下可用。

3. 深度休眠:此电源模式下即便是系统时钟也被禁用,所以在此模式下所有高频资源都不可用。不过,这些资源的当前状态不受影响,也就是说CPU寄存器、 SRAM等的当前状态不受影响。由于高频时钟被禁用,因此能节约开关消耗的功率。通常情况下,深度休眠模式提供低频时钟运行的选项,低频时钟可用来驱动定时器等低频资源。此外,该模式也允许开发人员使用I2C从设备等通信协议块,其无需器件自身生成时钟。由于进入此模式的主要方法就是禁用系统主时钟,因此这是可以实现的。然而,模块仍然可通电。该模式对功耗的影响主要在于片上所有时钟的静态功耗。

4.冬眠:在此模式下,所有时钟都关闭,包括低速振荡器。片上所有资源,除了用于外部事件触发唤醒的资源以外全都断电。由于本模式下几乎所有组件都断电,因此该模式能减少静态和动态功耗组件,从而实现最低功耗。

5.停止:顾名思义,停止模式就是所有外设断电,即使是RAM和CPU寄存器的内容也不保持。在PSoC 4等类似器件中,这种模式下仅保持IO引脚的状态。从这种模式下唤醒会进入芯片重启动。

当分析一款应用的功耗时,必须查看所有电源模式下的功耗情况。

必须明确某种模式下能提供唤醒源。举例来说,需要某种中断才能从休眠模式唤醒,在冬眠模式下则需要I2C地址匹配中断以唤醒器件。需要了解每种模式下有哪些资源工作,能提供什么唤醒资源。举例来说,系统中可用比较器中断作为唤醒源,在超出设定阈值情况下可用模拟输入唤醒系统。就图1所示的应用而言,唤醒需要采用GPIO中断或者甚至硬复位,因为RTC会随时运行,而且控制器不需要保持此前的状态。

冬眠和停止模式下,功耗可低至100nA。对于RTC本身而言,您会很容易找到功耗很低的RTC(仅消耗100-200nA)。假设控制器直接驱动LCD,我们可认为LCD的关闭状态功耗为零。

这就使得图1所示系统中的平均功耗在300nA的范围内。如果我们假设设计方案采用CR2032作为电源,电池容量约为225mAh。就300nA的电流来说,电池仅在器件始终处于断电模式下能支持70到80年的工作。

每次按下按键,控制器都会唤醒。这会将控制器的功耗提升到500μA-1mA的范围。假设功耗为1mA左右,控制器从RTC获取数据并显示在LCD 上。控制器执行这项工作只需很短的时间,但显示屏要保持较长工作时间(假设说显示屏亮起10秒钟确保用户看到数据)。作为直接驱动LCD,控制器必须保持较长的工作时间,也就是要消耗更多电荷。在此情况下,赛普拉斯的PSoC4等器件可提供低功耗模式,能让设备关闭所有其它外设,仅运行驱动LCD所需的模块。在这种器件中,LCD驱动运行在特定的低功耗模式下,这种模式被称为数字关联模式。其结果就是大幅减少电流消耗。

图2:各种状态下的电流消耗

每次按键都会经历如图2所示的电流曲线。曲线下方区域是单次按键的典型功耗。消耗的电荷计算如下:

Q = (1mA*1ms) + (20μA*10s)

根据上面的数据,我们可计算出给定电源能支持多少次按键。

工作模式下所花的时长非常重要,因为这种模式下耗电最大。一个选项是让MCU保持工作模式,但CPU时钟速度较低,从而降低工作模式下的耗电。不过,这会导致更高的平均功耗,因为工作模式所花的时间取决于时钟频率。此时由于MCU必须处于工作模式,因此功耗取决于MCU处理数据所花的时间。更快速的 MCU能很快完成任务,从而延长处于低功耗模式下的时间,也就能让系统减少功耗。系统设计人员可根据系统要求明确最佳配置。

在本系列文章的下一部分,我们将以更大型系统为例作讲解,并介绍如何降低平均功耗。此外,我们还将探讨一些降低平均功耗的系统级技巧。

SoC MCU 赛普拉斯 PSoC ADC 比较器 振荡器 LCD 电流 相关文章:

- 功率与控制的结合使LED照明方案灵活、简便(10-20)

- 以89C51单片机为控制核心的开关电源优化设计(07-25)

- 用于低功耗SoC设计的自适应电压调节技术(07-28)

- 满足多媒体处理器动态需求的电源管理技术(08-12)

- 嵌入式Linux的动态电源管理技术(09-03)

- Power Architecture许可开放飞思卡尔e200系列内核助力SoC设计(09-17)