全面剖析雷达电路的电磁干扰和EMC设计

好让它起止于同一个功能块内,即组装在同一屏蔽盒里。

b、数字电路与模拟电路必须分开组装,相互间的连接应加以隔离,必要时可用光电耦合器件将它们完全隔离。

c、传输高稳定信号的电缆,必要时给电缆再加屏蔽套,或选用半刚性电缆和刚性电缆。

d、电路和元器件排列应合理,不要使信号迂回,尽量减小输出输入及各种情况上的相互耦合。

e、尽量选用平面安装电路,不要大面积接地,它对电磁场的辐射抵制优于立体电路,可大大降低场辐射。

f、特别注意噪声电路,噪声元器件的装配位置,处理了它们的地线,例如:继电器、电源变压器、高功率大电流器件及高压脉冲电路等等。

g、不要在屏蔽体上安装大功率、大电流元件,防止它们的返回电流通过屏蔽体产生不必要的耦合干扰。

屏蔽设计

在电磁兼容的设计中,屏蔽体设计是非常重要的一个方面。屏蔽是抑制一切无关信号的重要手段,一般可分三种类型:静电屏蔽、磁屏蔽、电磁屏蔽。

1静电屏蔽

空间任何两个带电物体均可产生静电场,其中一方电压的变化必定会引起另一方的变化,产生静电祸合。静电藕合的机理是通过电路之间存在的电容拙合作用引起的。

克服静电荆合最好的方法是利用金属板作静电屏蔽体。把受干扰的两个源用金属板隔离开,或者把电路上的所有元器件安装在金属板的一边,如同表面安装电路那样,可获得良好的静电屏蔽。具体的屏蔽方法,尤其对杂散电容祸合作用的屏蔽,应该在设计初始阶段就全面加以考虑。

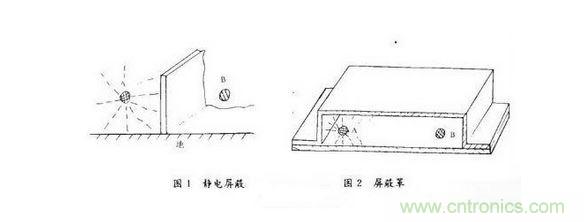

屏蔽方法:将一块金属板置于两个被屏蔽的电路中间,并使各金属板与地作电气连接,如图l所示。这样从一点发出的电力线均被屏蔽板挡住,即起到静电屏蔽作用。

也可作成屏蔽罩,如图2所示,也能获得好的屏蔽效果。由图2看出,A点的电力线也达不到B点,因此也能起到良好的静电屏蔽作用。

加大A、B距离,以减小杂散电容,也可减弱电容祸合作用,但这种方法受到体积限制,一般无法采用。特别要注意静电屏蔽体与地之间的接触必须良 好,若接触不好,屏蔽体与地之间将有电位差,影响屏蔽效果。因此要求屏蔽盒应作导电防腐处理,所用螺钉,铆钉等固定不宜太稀,尽量使电接触良好,减小接地 电阻,减小接地电感。

2磁屏蔽

电流在导线中流动,流过电感线圈和变压器时,其周围产生磁场,磁场通过电路中的互感来传播,电流产生的磁力线,通过互感在其它电路中感应出电压。

尤其在3KH:以下的低频条件下,主要干扰影响是由磁场引起的,但解决磁屏蔽往往既昂贵又困难。在雷达中,磁屏蔽主要针对电源变压器和高压调制器。一般低纹波电源的变压器常都采用坡莫合金加以屏蔽,否则达不到良好效果。

3电磁屏蔽

任何一种交流电路都会产生交变的电场和磁场。电磁屏蔽与电磁场的性质、变化频率、及辐射源和受感器之间的距离等有关。在雷达电子电路系统中,工 作频率一般都较高,在IKHz以上,一般可选用铝为电磁屏蔽材料。用切削工艺制成的铝屏蔽盒,对300MHz信号屏蔽隔离可达100dB以上。当频率 在]KHz以下,主要对磁场进行屏蔽,应选择高导磁率的材料。

在电子电路系统中,为了内部走线及取出放置电路方便,给屏蔽组装盒加有盖板,有时为了通风、散热等需要,在屏蔽板上打孔,开缝,造成屏蔽体出现 间断点,引起信号泄漏,形成干扰,设计者应认真考虑。正确排列元件的位置,使缝和孔不要切断感应电流,必要时可将孔改用截止波导管,使孔辐射进一步削弱。

屏蔽组装设计

除了屏蔽设计以外,组装技术也很重要,尤其是对射频系统的组装,更应细心设计。

一般应注意下面几点。

a、内部电路的屏蔽设计,应能防止电子线路自身的射频能量泄漏,同时也防止外界电磁能量对它的影响。

b、采取措施,防止电路级与级之间不必要的反馈和祸合。

c、对电源加滤波去锅措施,衰减抑制射频信号在电子组合内部和电子组合与组合之间传导。

d、射频接地电阻越小越好。

当然还必须兼顾体积、重量、成本等方面的要求。

当电路之间对寄生场的衰减要求较高时,用组装盒结构形式较好,它可作成单隔离室形式,也可设计成多个隔离室形式,即一个屏蔽盒,内分几个隔离 室,这样的组装

- 雷达电路的EMC分析(08-02)

- 电磁干扰滤波器解决方案综述(07-13)

- DVD数字视盘机电磁干扰设计(02-24)

- FID技术&医疗器械扰出“八级强震”(03-01)

- 滤波电容器的EMC设计(05-09)

- 医疗仪器设备中的EMC解决方案(05-23)