新型小电流接地故障选线装置的设计

时间:09-30

来源:互联网

点击:

2.3 采集板原理

图3中虚线框内的部分即为采样处理单元的硬件框图。它以C5402 DSP为CPU,主要由1)外围辅助电路,2)程序/数据存储器,3)模拟量输入通道,4)开关量输入/输出通道,5)通信串口,6)C5402与PC工控机通信接口电路等六部分组成。

选用C5402 DSP为CPU是为了减轻连续采样给系统带来的负担。例如采样速率为10 k,在不外加硬件缓冲设备的情况下,中断周期为1/10 k="100"μs而传统的诸如Windows、Linux等操作系统它们主要是针对多任务设计的,其中的调度子程序主要以平均分配时间片的方法来解决多任务,这个时间片的基值单位叫做全局变量jiffies,在传统操作系统中这个值一般在10 ms左右,显然这是很难满足我们要求的。一般情况下对应上述情况,普通采集板的处理办法就是外加FIFO。FIFO为先进先出存储器,AD顺序写入数据,用户可以同时顺序将数据实时地读出。FIFO通常应用的标志位为:“半满-HF”与“溢出-FF”,FIFO的操作在HF=0时,用户可以一次将采样数据连续读出,同时不间断AD向FIFO写入数据。如果FIFO的FF位为0,表示FIFO溢出,读出的数据将会丢失数据,所以用户必需保持FIFO不溢出。但是外加FIFO的这种方法只能暂缓中断的问题,不能根本解决问题。

下面以FIFO容量为1 k,具有8路A/D,采样率为10 k的普通采集板为例进行分析:

中断时每路采集到的点数N=512/8=64;

中断间隔时间T=64/10000=6.4 ms。

可见如果采样率这么高或是更高的话对于一般操作系统来说是很难稳定运行的。同时采用FIFO后还会产生另外一个问题,就是故障的实时判定。采用FIFO后必须每隔一段时间才能进行故障判定。在故障信号突变不明显时就很难准确地定位故障点,而对于本采集单元上述问题就不存在,因为TMS320VC5402采用增强的哈佛结构,8条内部总线使芯片的处理能力发挥到最大。可独立寻址的64 k数据空间和1 M程序空间,允许同时存取程序指令和数据。六级流水线操作保证了它的处理速度能达到 100 MIPS(每秒百万指令数)。这对于一般要求的采样速率是完全可以胜任的,可以对采集数据进行逐点计算从而大大提高了精度和准确度。

2.4 采集板与主机的通讯的实现

本系统是一个主从式的结构,主机为PC工控机,从机为TMS320VC5402 DSP,它们通过PC ISA总线建立连接。PC机可以通过C5402的HPI口读写其片内RAM存储单元,而C5402不能读写主机的存储单元,双方采用中断方式互相联络。传统的单片机与外部主机进行接口时,需要外扩必要的硬件电路。当单片机需要与主机共享RAM时,需在片外扩展RAM及触发、锁存等芯片,然后主机通过DMA方式访问该扩展RAM,这样一来主机可以随机或整块地访问、共享RAM。另外,在片外至少需要扩展一片锁存器使得单片机可以中断主机。TI的TMS320C5402 HPI接口将以上功能集成到DSP内部,使其与主机的连接变得非常简单。而且由于HPI是集成到片内的,主机可以达到很高的访问速度,满足了数字信号处理中高速度的要求。

在实际应用中,PC机要向C5402发送一些控制命令和数据,主要包括:1)采样命令,控制C5402采样的起停;2)参数修改命令,通知C5402修改参数及整定值;3)数据上传命令,通知C5402上传采样数据等。同时,C5402也要告知PC机自己所处的运行状态和所检测到的信息,主要包括:1)正常运行状态;2)故障启动状态。

为了实现上述的双向信息交流,可以在C5402的内部RAM中定义两个存储单元,一个是命令单元,用于存放PC机发给C5402的命令字;另一个是状态单元,用于存放标志C5402系统所处状态的状态字。另外,再从C5402内部RAM中划分出两个存储区,一个是Host区,用于存放PC机传给C5402的数据;另一个是Slave区,用于存放C5402要传给PC机的数据。当PC机要向C5402发送命令和数据时,先将命令字和数据分别写入命令单元和Host区,然后向C5402发出中断请求信号,C5402响应中断后将命令字和数据读出,并根据命令字完成相应的操作。PC机可以随时读取状态单元,以获取C5402系统的状态信息。正常运行时,C5402状态字的值为初始化值(0000H)。故障发生后,当C5402需要向PC机上传必要的数据信息时,先将状态字和数据分别写入状态单元和Slave区,然后向PC机发出中断请求,PC响应中断后将状态字和数据读出,并根据状态字完成相应的操作。

2.5 采集板的实验验证

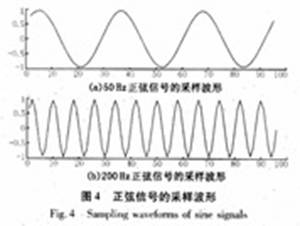

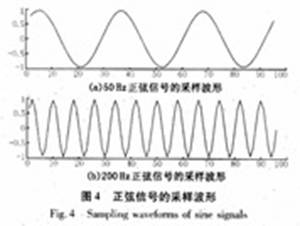

为了验证采样及处理单元工作的正确性,并可用于故障选线装置中,完成了以下实验。试验用信号由信号发生器产生:电平为-1 V~+1 V,频率分别为50 Hz和200 Hz的正弦信号。

试验中,用DSP的XF引脚产生A/D采样时钟信号,其采样频率由DSP的内部定时器设定,为1.6 kHz。对于200 Hz的输入信号,在一个周期采样8点;对于50 Hz的输入信号,在一个周期采样32点。采样数据先保存在DSP的内部RAM中,然后由工控机通过ISA总线读进来,并以文件的形式保存到硬盘上,最后用MATLAB将波形显示出来,如图4(a)和图4(b)。

从这两个图可以看出,采样恢复波形与原始波形相吻合,而且很光滑。通过以上试验可以肯定,本采样及处理单元的设计是成功的。

图3中虚线框内的部分即为采样处理单元的硬件框图。它以C5402 DSP为CPU,主要由1)外围辅助电路,2)程序/数据存储器,3)模拟量输入通道,4)开关量输入/输出通道,5)通信串口,6)C5402与PC工控机通信接口电路等六部分组成。

选用C5402 DSP为CPU是为了减轻连续采样给系统带来的负担。例如采样速率为10 k,在不外加硬件缓冲设备的情况下,中断周期为1/10 k="100"μs而传统的诸如Windows、Linux等操作系统它们主要是针对多任务设计的,其中的调度子程序主要以平均分配时间片的方法来解决多任务,这个时间片的基值单位叫做全局变量jiffies,在传统操作系统中这个值一般在10 ms左右,显然这是很难满足我们要求的。一般情况下对应上述情况,普通采集板的处理办法就是外加FIFO。FIFO为先进先出存储器,AD顺序写入数据,用户可以同时顺序将数据实时地读出。FIFO通常应用的标志位为:“半满-HF”与“溢出-FF”,FIFO的操作在HF=0时,用户可以一次将采样数据连续读出,同时不间断AD向FIFO写入数据。如果FIFO的FF位为0,表示FIFO溢出,读出的数据将会丢失数据,所以用户必需保持FIFO不溢出。但是外加FIFO的这种方法只能暂缓中断的问题,不能根本解决问题。

下面以FIFO容量为1 k,具有8路A/D,采样率为10 k的普通采集板为例进行分析:

中断时每路采集到的点数N=512/8=64;

中断间隔时间T=64/10000=6.4 ms。

可见如果采样率这么高或是更高的话对于一般操作系统来说是很难稳定运行的。同时采用FIFO后还会产生另外一个问题,就是故障的实时判定。采用FIFO后必须每隔一段时间才能进行故障判定。在故障信号突变不明显时就很难准确地定位故障点,而对于本采集单元上述问题就不存在,因为TMS320VC5402采用增强的哈佛结构,8条内部总线使芯片的处理能力发挥到最大。可独立寻址的64 k数据空间和1 M程序空间,允许同时存取程序指令和数据。六级流水线操作保证了它的处理速度能达到 100 MIPS(每秒百万指令数)。这对于一般要求的采样速率是完全可以胜任的,可以对采集数据进行逐点计算从而大大提高了精度和准确度。

2.4 采集板与主机的通讯的实现

本系统是一个主从式的结构,主机为PC工控机,从机为TMS320VC5402 DSP,它们通过PC ISA总线建立连接。PC机可以通过C5402的HPI口读写其片内RAM存储单元,而C5402不能读写主机的存储单元,双方采用中断方式互相联络。传统的单片机与外部主机进行接口时,需要外扩必要的硬件电路。当单片机需要与主机共享RAM时,需在片外扩展RAM及触发、锁存等芯片,然后主机通过DMA方式访问该扩展RAM,这样一来主机可以随机或整块地访问、共享RAM。另外,在片外至少需要扩展一片锁存器使得单片机可以中断主机。TI的TMS320C5402 HPI接口将以上功能集成到DSP内部,使其与主机的连接变得非常简单。而且由于HPI是集成到片内的,主机可以达到很高的访问速度,满足了数字信号处理中高速度的要求。

在实际应用中,PC机要向C5402发送一些控制命令和数据,主要包括:1)采样命令,控制C5402采样的起停;2)参数修改命令,通知C5402修改参数及整定值;3)数据上传命令,通知C5402上传采样数据等。同时,C5402也要告知PC机自己所处的运行状态和所检测到的信息,主要包括:1)正常运行状态;2)故障启动状态。

为了实现上述的双向信息交流,可以在C5402的内部RAM中定义两个存储单元,一个是命令单元,用于存放PC机发给C5402的命令字;另一个是状态单元,用于存放标志C5402系统所处状态的状态字。另外,再从C5402内部RAM中划分出两个存储区,一个是Host区,用于存放PC机传给C5402的数据;另一个是Slave区,用于存放C5402要传给PC机的数据。当PC机要向C5402发送命令和数据时,先将命令字和数据分别写入命令单元和Host区,然后向C5402发出中断请求信号,C5402响应中断后将命令字和数据读出,并根据命令字完成相应的操作。PC机可以随时读取状态单元,以获取C5402系统的状态信息。正常运行时,C5402状态字的值为初始化值(0000H)。故障发生后,当C5402需要向PC机上传必要的数据信息时,先将状态字和数据分别写入状态单元和Slave区,然后向PC机发出中断请求,PC响应中断后将状态字和数据读出,并根据状态字完成相应的操作。

2.5 采集板的实验验证

为了验证采样及处理单元工作的正确性,并可用于故障选线装置中,完成了以下实验。试验用信号由信号发生器产生:电平为-1 V~+1 V,频率分别为50 Hz和200 Hz的正弦信号。

试验中,用DSP的XF引脚产生A/D采样时钟信号,其采样频率由DSP的内部定时器设定,为1.6 kHz。对于200 Hz的输入信号,在一个周期采样8点;对于50 Hz的输入信号,在一个周期采样32点。采样数据先保存在DSP的内部RAM中,然后由工控机通过ISA总线读进来,并以文件的形式保存到硬盘上,最后用MATLAB将波形显示出来,如图4(a)和图4(b)。

从这两个图可以看出,采样恢复波形与原始波形相吻合,而且很光滑。通过以上试验可以肯定,本采样及处理单元的设计是成功的。

电流 电容 电压 电路 滤波器 电阻 仿真 DSP Maxim ADC Linux 总线 MIPS 单片机 信号发生器 相关文章:

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)