端接未使用的低电压差分信号总线输入

时间:06-11

来源:互联网

点击:

低电压差分信号(LVDS)是EIA/TIA-644标准中定义的总线技术。这种技术的特点是通过使用差分信号有较低的电压摆幅,从而具备Gbps数据速率的能力。这种技术相对单端技术的优势包括消除差分线路上传输的两个平衡信号的电磁干扰,加强了抗噪声能力。但是,当并非所有的LVDS输入都使用的时候,我们必须注意,因为浮接输入端可能会引入噪声从而导致数据错误。所以当LVDS输入端不使用的时候需要进行合适的端接。

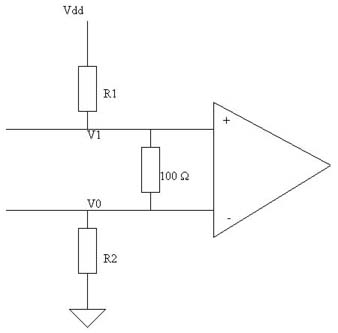

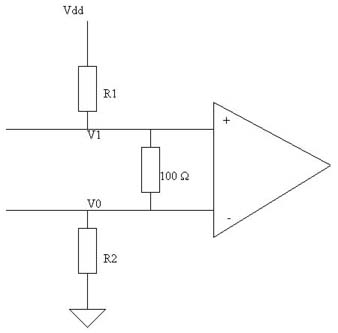

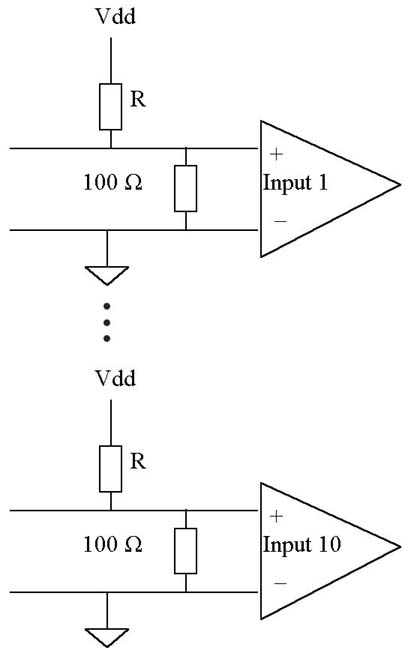

图1为不使用的LVDS输入端端接方案举例。

不使用的LVDS输入端将使用差分信号端间摆幅大于200mV的差分输入电压进行端接。

假设理想的共模电压为1.25V,且差分信号端间需要400mV的电压,那么所需的电流为4mA。因此V1电压为1.45V,V0电压为1.05V。

若Vdd为2.5V,

R1=(Vdd-V1)/4mA=(2.5-1.45)/4mA=262.5Ω

R2=V0/4mA=1.05/4mA=262.5Ω

若Vdd为3.3V,

R1=(Vdd-V1)/4mA=(3.3-1.45)/4mA=462.5Ω

R2=V0/4mA=1.05/4mA=262.5Ω

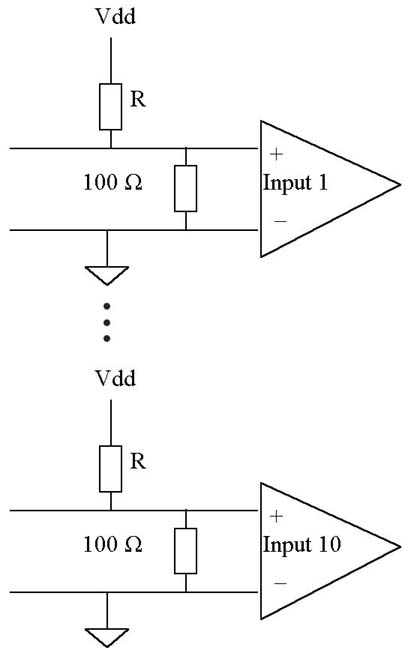

大多数LVDS输入的共模范围很广。例如,典型输入共模电压为1.25V的网络器件其输入共模范围可能为0~1.8V。因此,只要在器件共模范围内,信号端间的电压差大于200mV,未使用的LVDS输入端就可以正确地被端接。换句话说,下面的端接方式也是可行的。

若Vdd=2.5V,

R=(Vdd-0.4)/4mA=(2.5-0.4)/4mA=525Ω

或 R=1kΩ,可以得到差模电压约为227mV(>200mV)

这种端接的方案减少了所需电阻的个数。不足之处是在印刷电路板上无法接触LVDS输入的负端接端。

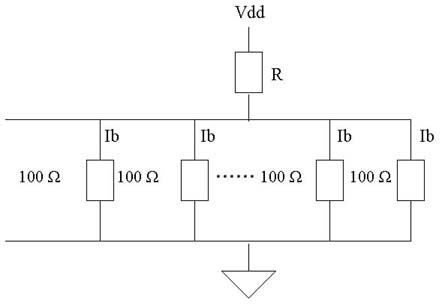

使用同样的端接方案,如果需要考虑到所占用的板空间,可以采用一组LVDS输入端接的方法。例如,10个正端子可以使用一个上拉电阻上拉。选择这个上拉电阻值的时候,要考虑到保证所有差分端子间的电压差大于200mV。

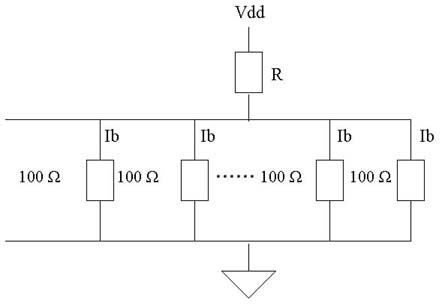

这种方法组成图4所示的等效输入电阻网络。

若Vdd=2.5V,R可以为100Ω,提供220mV的差模电压,计算公式如下;一组有10个正端子的网络有10个并联电阻,其等效阻抗为100Ω。因此总电流为:

I=Vdd/(R+10)=2.5/(100+10)=22.73mA

根据基尔霍夫电流定律,支路电流为:

Ib=22.73/10=2.273mA

因此每个端子间的差模电压为:

Vdiff=2.273mA×100=227.3mV

Vdiff大于最小差模电压幅度200mV,所以这种端接方式可行。

注意,这些公式中使用的电阻值不是标准的电阻值。

图1为不使用的LVDS输入端端接方案举例。

不使用的LVDS输入端将使用差分信号端间摆幅大于200mV的差分输入电压进行端接。

假设理想的共模电压为1.25V,且差分信号端间需要400mV的电压,那么所需的电流为4mA。因此V1电压为1.45V,V0电压为1.05V。

若Vdd为2.5V,

R1=(Vdd-V1)/4mA=(2.5-1.45)/4mA=262.5Ω

R2=V0/4mA=1.05/4mA=262.5Ω

若Vdd为3.3V,

R1=(Vdd-V1)/4mA=(3.3-1.45)/4mA=462.5Ω

R2=V0/4mA=1.05/4mA=262.5Ω

大多数LVDS输入的共模范围很广。例如,典型输入共模电压为1.25V的网络器件其输入共模范围可能为0~1.8V。因此,只要在器件共模范围内,信号端间的电压差大于200mV,未使用的LVDS输入端就可以正确地被端接。换句话说,下面的端接方式也是可行的。

若Vdd=2.5V,

R=(Vdd-0.4)/4mA=(2.5-0.4)/4mA=525Ω

或 R=1kΩ,可以得到差模电压约为227mV(>200mV)

这种端接的方案减少了所需电阻的个数。不足之处是在印刷电路板上无法接触LVDS输入的负端接端。

使用同样的端接方案,如果需要考虑到所占用的板空间,可以采用一组LVDS输入端接的方法。例如,10个正端子可以使用一个上拉电阻上拉。选择这个上拉电阻值的时候,要考虑到保证所有差分端子间的电压差大于200mV。

这种方法组成图4所示的等效输入电阻网络。

若Vdd=2.5V,R可以为100Ω,提供220mV的差模电压,计算公式如下;一组有10个正端子的网络有10个并联电阻,其等效阻抗为100Ω。因此总电流为:

I=Vdd/(R+10)=2.5/(100+10)=22.73mA

根据基尔霍夫电流定律,支路电流为:

Ib=22.73/10=2.273mA

因此每个端子间的差模电压为:

Vdiff=2.273mA×100=227.3mV

Vdiff大于最小差模电压幅度200mV,所以这种端接方式可行。

注意,这些公式中使用的电阻值不是标准的电阻值。

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)

- 高效地驱动LED(04-23)